Запоминающие устройства для хранения оперативной информации

Область применения относительно дорогостоящих статических ЗУ в системах обработки информации определяется их высоким быстродействием. В частности, они широко применяются в кэш-памяти, которая при сравнительно малой емкости должна иметь максимальное быстродействие.

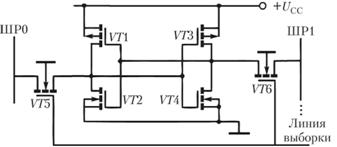

Статические ОЗУ, как правило, имеют структуру 2DM. В качестве ЗЭ в них используются триггеры с цепями установки и сброса (рис. 4.7).

Рис. 4.7. Схема триггерного запоминающего элемента статических ЗУ

Такой триггер в КМОП-технологии содержит 6 транзисторов. На четырех выполняется сам ЗЭ, а два служат для выборки ЗЭ и чтения/заниси. Комплементарные пары транзисторов VT1, VT2 и VT3, VT4 работают противофазно: если открыт один транзистор, другой – закрыт. Они составляют плечи триггера, которые также работают противофазно. Пусть, например, в левом плече транзистор VT1 открыт. Тогда высокий потенциал от +UCC через VT подается на затворы транзисторов VT3 и VT4. При этом транзистор VT3 запирается, a VT4 – открывается. Низкий потенциал корпуса через открытый VT4 подается на затворы транзисторов VT1 и VT2 и поддерживает открытое состояние VT1 и закрытое VT2. Если же транзистор V73 будет открыт, то будут закрыты транзисторы VT1 и VTA, а транзистор VT2 – открыт, поддерживая открытое состояние транзистора VT3. Таким образом, ЗЭ может находиться только в двух устойчивых состояниях. Если открыт транзистор VTI, то ЗЭ хранит лог. 1, если же открыт транзистор 173 – то лог. 0. Транзисторы VT5 и VT6 своими затворами подключены к линии выборки и открываются при подаче в нес высокого потенциала. При открытии транзисторов VT5 и VIБ потенциалы с плечей ЗЭ поступают на разрядные шины ШР1 и ШР0.

Для того чтобы перевести ЗЭ в противоположное состояние, на шину ШР1 или ШР0 подается потенциал лог. "0", а в линию выборки – высокий потенциал, открывающий транзисторы VT5 и VT6. Пусть, например, ЗЭ хранит "1", т.е. VT1 и VT4 – открыты, a VT2 и 173 – закрыты. Подача лог. 0 от шины ШРО через открытый VT5 на затворы транзисторов V73 и VT4 приводит к запиранию транзистора VT4 и отпиранию V73. В результате высокий уровень напряжения +UCC, поступивший через V73 на затворы VT1 и VT2, закрывает VT1 и отпирает VT2. Таким образом, триггер переходит в противоположное состояние, соответствующее хранению лог. 0.

Статические ОЗУ энергозависимы – при снятии питания информация в триггерных ЗЭ теряется. Можно придать им энергонезависимость с помощью резервного источника питания. Это наиболее пригодно для ЗУ на КМОП-элементах, так как они в режиме хранения потребляют чрезвычайно малую мощность.

Как известно, ИС, выполненные но КМОП-технологи, не способны работать на емкостную нагрузку (см. параграф 3.4), поэтому одним из направлений развития статических ЗУ является совмещение КМОП и биполярной технологий в одной ИС. В таких микросхемах матрица ЗЭ выполняется по КМОП-технологии, а выходные каскады – по биполярной технологии, обеспечивающей более высокое быстродействие микросхемы и эффективную работу на емкостную нагрузку.

Динамические ЗУ

В динамических ЗУ данные хранятся в виде зарядов емкостей МОП-структур, и основой ЗЭ является просто конденсатор небольшой емкости. Такой ЗЭ значительно проще триггерного, содержащего 6 транзисторов, что позволяет разместить на кристалле намного больше ЗЭ. В то же время конденсатор со временем неизбежно теряет свой заряд, и хранение данных требует их периодической регенерации (несколько миллисекунд).

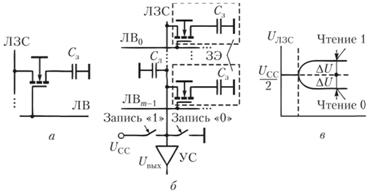

Электрическая схема однотранзисторного ЗЭ показана на рис. 4.8, а. Запоминающий конденсатор С3 образуется между стоком транзистора, не имеющего внешнего вывода, и подложкой, т.е. корпусом. Лог . 1 соответствует заряженной емкости, а лог. О – разряженной. Транзистор отключает запоминающий конденсатор от линии записи/считывания (ЛЗС) или подключает его к ней.

Рис. 4.8. Динамическое ЗУ:

запоминающий элемент (а); фрагмент схемы (б); график, поясняющий процесс считывания (в)

ЗЭ образуют матрицу, один столбец которой показан на рис. 4.8, б. Ключевые транзисторы своими затворами подключены к линиям выборки (ЛВ), которые образуют строки матрицы ЗЭ. Истоки транзисторов, которые образуют столбцы матрицы, подключены к ЛЗС. Таким образом, ЗЭ включаются на пересечении строк и столбцов.

В режиме хранения ключевой транзистор заперт. При записи на затвор транзистора выбранного ЗЭ подается отпирающее напряжение, транзистор открывается, и через один из записывающих ключей емкость С3 либо заряжается до напряжения Ucc (лог. 1), либо разряжается на корпус (лог. 0). При чтении транзистор открывается и емкость подключается к ЛЗС. При этом в зависимости от того, заряжена или разряжена емкость, потенциал ЛЗС изменяется по-разному. ЛЗС сама имеет некоторую емкость Сл, которая перед подключением к ней ЗЭ заряжается до потенциала, равного половине уровня питающего напряжения (рис. 4.8, в). Если емкость ЗЭ была заряжена (лог. 1), то часть заряда перетекает в ЛЗС и ее потенциал повышается. Если же ЗЭ был разряжен (лог. 0), то часть заряда с ЛЗС перетекает в емкость ЗЭ и потенциал ЛЗС понижается. Усилитель считывания УС воспринимает потенциал ЛЗС и формирует выходной сигнал.

Как видно из описанных процессов, заряд ЗЭ при чтении изменяется, поэтому после чтения его необходимо восстановить. Для этого в микросхеме имеются специальные усилители-регенераторы, которые автоматически по остаточному заряду С3 определяют, каков был заряд ЗЭ до чтения. Если ЗЭ хранил лог. 1, то на ЛЗС устанавливается высокий уровень, и С3 дозаряжается до единичного потенциала, если же ЗЭ хранил лог. 0, на ЛЗС устанавливается нулевой уровень и С3 полностью разряжается.

Усилители-регенераторы обеспечивают восстановление данных не только после операции чтения, но и в режиме периодической регенерации данных всех ЗЭ. В каждом столбце матрицы ЗЭ есть свой усилитель-регенератор, поэтому регенерация осуществляется построчно и одновременно для всех ЗЭ одной строки. Режим строчной регенерации осуществляется с помощью циклов чтения по всем строкам матрицы ЗЭ. При этом процесс не сопровождается выдачей данных на выходные буферы, а целиком проходит внутри ЗУ. Используются только адреса строк, а адреса столбцов не требуются.

Модуль памяти на основе динамических ЗУ составлен из одноразрядных микросхем, число которых равно разрядности хранимых слов. Относительно входных сигналов все микросхемы включены параллельно. В рабочем режиме модулем управляет процессор, а в режиме регенерации – специальный контроллер. В некоторых ЗУ схемы регенерации данных реализованы на самом кристалле памяти и контроллер регенерации не нужен. Такие ЗУ называют квазистатическими.

Современные микропроцессоры характеризуются высоким быстродействием. Это требует увеличения скорости работы ОЗУ, обменивающихся информацией с процессорами. Особенно остро эта задача стоит перед разработчиками динамических ОЗУ, которые благодаря максимальной информационной емкости и низкой стоимости занимают ведущее место в составе памяти компьютеров. В последнее время предложен ряд вариантов динамических ОЗУ повышенного быстродействия. Методы, использованные в этих ОЗУ, основаны на предположении о кучности адресов при обращениях к ОЗУ. Действительно, команды программы обычно располагаются в ОЗУ компактно, команда за командой. Точно так же располагаются и массивы данных.

Архитектура, технология и схемотехника полупроводниковых ЗУ постоянно развиваются. Поколения динамических ЗУ сменяются приблизительно каждые пять лет. В 1990 г. доминировали ЗУ емкостью 1 Мбит, в начале этого века в основном использовались микросхемы ЗУ с емкостью 64 и 128 Мбит. К 2010 г. ведущие фирмы-производители микросхем памяти освоили выпуск чипов емкостью в 4 Гбита. Число транзисторов в них стало составлять уже более 4 млрд. Это позволило создавать модули оперативной памяти емкостью в 4 Гбайт при установке чипов на одной стороне модуля памяти и 8 Гбайт – при двухсторонней.