Существуют несколько типов и видов ячеек, отличающихся по технологии и функционированию. Рассмотрим основные.

ЛЕКЦИЯ 4

ФУНКЦИОНИРОВАНИЕ ФЛЭШ–ПАМЯТИ, РАЗНОВИДНОСТИ ФЛЭШ–ПАМЯТИ.

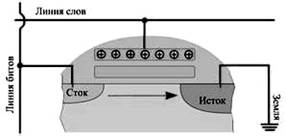

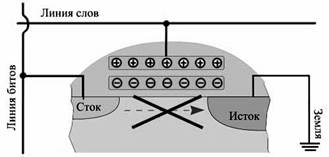

Рассмотрим, как работает ячейка (Таблица 1).

| При чтении, в отсутствие заряда на "плавающем" затворе, под воздействием положительного заряда на управляющем затворе, образуется n-канал в подложке между истоком и стоком, и возникает ток – состояние «единица». |

| Наличие заряда на "плавающем" затворе меняет вольтамперные характеристики транзистора таким образом, что при обычном, для чтения, напряжении, канал не появляется, и тока между истоком и стоком ток не возникает – состояние «ноль». |

| При программировании, на сток и управляющий затвор подаётся высокое напряжение, причём на управляющий затвор напряжение подаётся приблизительно в два раза выше. "Горячие" электроны из канала инжектируются на плавающий затвор и изменяют вольт - амперные характеристики транзистора. Такие электроны называют "горячими" за то, что они обладают высокой энергией, достаточной для преодоления потенциального барьера, создаваемого тонкой плёнкой диэлектрика. |

| При стирании высокое напряжение подаётся на исток. На управляющий затвор подаётся высокое отрицательное напряжение. Электроны туннелируют на исток. |

Процедуры стирания и записи сильно изнашивают ячейку флэш-памяти, поэтому в современных микросхемах применяются специальные алгоритмы, оптимизирующие процесс стирания-записи, а также алгоритмы, обеспечивающие равномерное использование всех ячеек в процессе функционирования.

Поведение транзистора зависит от количества электронов на "плавающем" затворе. "Плавающий" затвор играет главную роль, он хранит запрограммированное значение.

В прошлом, помещение заряда на "плавающий" затвор в такой ячейке, как правило, производилось методом инжекции "горячих" электронов (CHEI - channel hot electrons injection), а снятие заряда осуществляется методом квантомеханического туннелирования Фаулера-Нордхейма (Fowler-Nordheim (FN)).

В настоящее время выпускается флэш-память, в которой и запись и считывание осуществляется методом FN, что позволяет уменьшить энергопотребление, увеличить срок службы.

Существуют несколько типов и видов ячеек, отличающихся по технологии и функционированию. Рассмотрим основные.

Однотранзисторная ячейка памяти «STACKED GATE CELL».

По сути это простейшая ячейка с плавающим затвором, на примере которой мы рассматривали принципы действия и организации флэш-памяти. Ячейка флэш-памяти Stacked Gate Cell (ячейки с многослойным затвором), имеет наиболее простую реализацию. Кроме того, именно на ее базе (путем модификаций и усложнений) созданы все известные ныне разновидности ячеек флэш-памяти.

Однотранзисторные ячейки имеют ряд существенных недостатков. Главный недостаток — плохая масштабируемость. Дело в том, что при организации массива памяти каждая ячейка памяти (транзистор) подключается к двум перпендикулярным шинам: управляющие затворы — к шине, называемой линией слов, а стоки — к шине, называемой битовой линией. Вследствие наличия в схеме высокого напряжения при записи методом инжекции горячих электронов все линии — слов, битов и истоков — необходимо располагать на достаточно большом расстоянии друг от друга для обеспечения требуемого уровня изоляции, что, естественно, сказывается на ограничении объема флэш-памяти.

Другим недостатком однотранзисторной ячейки памяти является наличие эффекта избыточного удаления заряда с плавающего затвора, который не может компенсироваться процессом записи. В результате на плавающем затворе образуется положительный заряд и транзистор остается всегда в открытом состоянии.

Двухтранзисторная ячейка памяти «TWO TRANSISTOR THIN OXIDE CELL».

В этом типе вместо одного в ячейке используются два транзистора, что и отражено в названии: двухтранзисторная ячейка с тонким слоем окисла. Такая структура позволяет избавиться от некоторых недостатков предшественника. Все операции в двухтранзисторной ячейке с плавающим затвором («Two Transistor Thin Oxide Cell») основаны на эффекте туннелирования.

Для того чтобы избежать недостатков однотранзисторных ячеек памяти, используют различные модификации ячеек памяти, однако главный базовый элемент — транзистор с плавающим затвором — остается в любом варианте ячейки памяти. Одним из модифицированных вариантов ячейки памяти является двухтранзисторная ячейка, содержащая обычный транзистор и транзистор с плавающим затвором (Рис.1.в). Обычный транзистор используется для изоляции транзистора с плавающим затвором от битовой линии.

Рис. 1.в. Двухтранзисторная ячейка памяти и ее обозначение.

Преимущество двухтранзисторной ячейки памяти заключается в том, что с ее помощью можно создавать более компактные и хорошо масштабируемые микросхемы памяти, поскольку в данном случае транзистор с плавающим затвором изолируется от битовой линии. Кроме того, в отличие от однотранзисторной ячейки памяти, где для записи информации используется метод инжекции горячих электронов, в данном случае и для записи, и для стирания информации применяется метод квантового туннелирования Фаулера-Нордхейма, что позволяет снизить напряжение, необходимое для операции записи.

«SST CELL».

Если названия предыдущих типов ячеек отражают физическую суть, то название SST ячеек образовано от названия компании-производителя — «Silicon Storage Technology».

Ячейки памяти SST получили широкое распространение.

В транзисторе SST-ячейки изменены формы плавающего и управляющего затворов (Рис. 2). Управляющий затвор выровнен своим краем с краем стока, а его изогнутая форма дает возможность разместить плавающий затвор частично под ним и одновременно над областью истока. Такое расположение плавающего затвора позволяет, с одной стороны, упростить процесс помещения на него заряда методом инжекции горячих электронов, а с другой стороны, упростить процесс снятия заряда за счет эффекта туннелирования Фаулера-Нордхейма.

Рис. 2. Структура SST-ячейки памяти.

При снятии заряда туннелирование электронов происходит не в область истока, как у обычной однотранзисторной ячейки, а в область управляющего затвора. Для этого на управляющий затвор подается высокое положительное напряжение. Под воздействием электрического поля, создаваемого управляющим затвором, происходит туннелирование электронов с плавающего затвора, чему способствует его изогнутая к краям форма.

При помещении заряда на плавающий затвор сток заземляется, а к истоку и к управляющему затвору подается положительное напряжение. Управляющий затвор формирует при этом канал проводимости, а напряжение между стоком и истоком «разгоняет» электроны, сообщая им энергию, достаточную для преодоления потенциального барьера, то есть для туннелирования на плавающий затвор.

SST-ячейки объединены вдоль линий слов (страницы) и линий битов (секторы). Страницей называют пару слов (четные и нечетные биты), связанных общим истоком. Удаляется страница как единый элемент.

Процесс удаления заключается в снятии с плавающего затвора отрицательного заряда за счет эффекта туннелирования Фаулера - Нордхейма между управляющей и плавающей базами. При программировании возникает обратная задача: необходимо сообщить плавающей базе отрицательный заряд. Для этого применяется эффект горячих электронов.

Многоуровневые ячейки памяти (MLC - Multi Level Cell).

Как уже говорилось ранее, flash-память – это транзистор с плавающим затвором, который позволяет хранить электроны. Поведение транзистора зависит от количества электронов. Операция программирования (заряд плавающего затвора) создает поток электронов между истоком и стоком транзистора. Часть этих электронов набирает достаточное количество энергии, чтобы преодолеть барьер диэлектрика и оказаться запертой на плавающем затворе. Если заряд плавающего затвора у однобитного транзистора меньше 5000 электронов, то это означает, что ячейка хранит логическую единицу, а если заряд больше 30000 электронов, то – ноль. Заряд ячейки вызывает изменение порогового напряжения транзистора, и при операции чтения измеряется величина этого порогового напряжения, а по нему определяется количество заряда на плавающем затворе.

На Рис.2.а показано распределение пороговых напряжений для массива из полумиллиона ячеек. После выполнения операции стирания или программирования каждой ячейки этого массива было проведено измерение порогового напряжения с результатами, представленными в виде гистограммы на рисунке. Стертые ячейки (логическая единица) имели порог 3.1В, в то время как запрограммированные (логический ноль) имели пороговое напряжение более 5В.

Рис.2.а. Распределение пороговых напряжений для одинарных ячеек.

Возможность сохранять заряд на ячейке дает возможность сохранять несколько бит на одной ячейке. Flash-ячейка является аналоговым запоминающим устройством, а не цифровым. Она хранит заряд (квантованный с точностью до одного электрона), а не биты. Поэтому, используя контролируемый метод программирования, на плавающий затвор можно поместить точное количество заряда. Если получится устанавливать заряд в одно из четырех состояний, то можно запрограммировать два бита данных на одной ячейке. Каждое из четырех состояний соответствует одному из двухбитных наборов.

На Рис.2.б показано распределение порогового напряжения для полумиллиона ячеек, способных хранить два бита данных. После стирания или точного программирования одного из трех состояний (трех, потому что одно состояние получается при стирании) были измерены величины пороговых напряжений и результаты помещены в виде гистограммы на рисунок. Заметим, что точное управление зарядом позволило двум средним состояниям сузить разброс напряжений до 0.3В, что соответствует 3000 электронов.

Рис.2.б. Распределение пороговых напряжений для мульти ячеек.

Большие плотности битов на одну ячейку возможны только при более точном размещении заряда на плавающий затвор. Для трех бит на ячейку потребуется программирование 8-ми различных состояний заряда, для четырех – 16-ти состояний. В общем, количество состояний равно 2 в степени N, где N – требуемое количество бит.

Возможность размещения точного количества заряда, а потом его точного считывания требует новых знаний в области физических основ работы ячейки памяти, а также устройства всего массива памяти в целом. Для этого необходимо решить три основные задачи:

· Точное размещение заряда: программирование ячейки flash-памяти должно очень хорошо контролироваться (что требует детального изучения физики программирования). Это значит, что во время программирования нужно подводить к ячейке ток на строго определенное время.

· Точное чтение количества заряда: операция чтения MLC-памяти – это аналого-цифровое преобразование заряда, сохраненного в ячейке, в цифровые данные (новое решение для устройств памяти).

· Надежное хранение заряда: для сохранения заряда на долгое время ставилась цель сделать его утечку меньше одного электрона за день.

В настоящее время эти задачи решены на практике, мульти ячейки широко используются в различных устройствах флэш-памяти.

Следует отметить проблемы реализации связанные с устранением шума и постепенной утечкой электронов при продолжительном хранении. Возникает задача поиска предельного числа бит, которое способна хранить многоуровневая ячейка, обеспечивая при этом надежную работу. Эта задача решается до сих пор.

Ячейки MLC активно разрабатываются компанией Intel, поэтому технология памяти на основе MLC-ячеек получила название Intel StrataFlash.

Основные преимущества MLC:

· Более низкое соотношение $/МБ.

· При равном размере микросхем и одинаковом техпроцессе "обычной" и MLC-памяти, последняя способна хранить больше информации (размер ячейки тот же, а количество хранимых в ней бит - больше).

· На основе MLC создаются микросхемы большей емкости, чем на основе однобитных ячеек.

Основные недостатки MLC:

· Снижение надёжности, по сравнению с однобитными ячейками, и, соответственно, необходимость встраивать более сложный механизм коррекции ошибок (чем больше бит на ячейку - тем сложнее механизм коррекции ошибок).

· Быстродействие микросхем на основе MLC зачастую ниже, чем у микросхем на основе однобитных ячеек.

· Хотя размер MLC-ячейки такой же, как и у однобитной, дополнительно тратится место на специфические схемы чтения/записи многоуровневых ячеек.

Архитектуры флэш-памяти.

Очевидно, что для того, чтобы перейти от отдельных ячеек к массиву памяти, их надо как то объединить. Основные типы соединений ячеек в массивы памяти на сегодняшний день – это NOR (ИЛИ-НЕ) и NAND (И - НЕ).

Тип соединения NOR (ИЛИ-НЕ) предполагает подключение ячейки к двум перпендикулярным линиям - битов и слов (Рис .3).

Если хотя бы один из транзисторов проводит ток, линия битов переходит в состояние «0». А с помощью линии слов происходит выбор читаемой ячейки. Все ячейки памяти NOR подключены к битовым линиям параллельно.

Рис. 3. Соединения ячеек.

Рис. 3. Соединения ячеек.

Второй тип организации - NAND (И - НЕ) (Рис. 3) предусматривает переход битовой линии в состояние «0», если ток проводят все транзисторы. Ячейки в данном случае подсоединяются к битовой линии сериями. Основная специфика — архитектура размещения ячеек и их контактов. В отличие от NOR, здесь имеется контактная матрица, в пересечениях строк и столбцов которой располагаются транзисторы. Это сравнимо с пассивной матрицей в дисплеях. Чипы этого типа более компактны. Недостатки заключаются в более низкой по сравнению с NOR скорости работы в операциях побайтового произвольного доступа. Для преодоления низкой скорости чтения используется встроенный кэш.

На основе основных типов соединения ячеек формируются архитектуры флэш-памяти.

Существует несколько типов архитектур (организаций соединений между ячейками) флэш-памяти (Таблица 2).

Таблица 2. Архитектуры флэш-памяти.

| NOR (NOT OR, ИЛИ-НЕ) | |||

| Характеристики: Интерфейс параллельный. Произвольное чтение и запись. Преимущества: быстрый произвольный доступ, возможность побайтной записи. Недостатки: относительно медленная запись и стирание. Из перечисленных здесь типов имеет наибольший размер ячейки, а потому плохо масштабируется. Единственный тип памяти, работающий на двух разных напряжениях. Идеально подходит для хранения кода программ (PC BIOS, сотовые телефоны), идеальная замена EEPROM. | ||

| Основные производители: AMD, Intel, Sharp, Micron, Ti, Toshiba, Fujitsu, Mitsubishi, SGS-Thomson, STMicroelectronics, SST, Samsung, Winbond, Macronix, NEC, UMC. | |||

| Программирование: методом инжекции "горячих" электронов Стирание: метод FN. | |||

| NAND (NOT AND, И-НЕ) | |||

.gif)

| Характеристики: Доступ произвольный, но небольшими блоками, наподобие кластеров жёсткого диска. В связи с этим появляется шина «Линия выборки». Последовательный интерфейс. Преимущества: быстрые запись и стирание, небольшой размер блока. Недостатки: относительно медленный произвольный доступ, невозможность побайтной записи. Наиболее подходящий тип памяти для приложений, ориентированных на блочный обмен: MP3 плееров, цифровых камер и в качестве заменителя жёстких дисков. | ||

| Основные производители: Toshiba, AMD/Fujitsu, Samsung | |||

| Программирование: метод FN. Стирание: метод FN. | |||

| Таблица 2. Архитектуры флэш-памяти (продолжение). AND (И) | |||

| Характеристики: Доступ к ячейкам последовательный, архитектурно напоминает NOR и NAND, комбинирует их лучшие свойства. Небольшой размер блока, возможно быстрое мультиблочное стирание. Подходит для потребностей массового рынка. | ||

| Основные производители: Hitachi и Mitsubishi Electric. | |||

| Программирование: метод FN. Стирание: метод FN. | |||

| Di NOR (Divided bit-line NOR), ИЛИ-НЕ с разделёнными разрядными линиями. | |||

| Характеристики: Тип памяти, комбинирующий свойства NOR и NAND. Доступ к ячейкам произвольный. Использует особый метод стирания данных, предохраняющий ячейки от пережигания (что способствует большей долговечности памяти). Размер блока в DiNOR всего лишь 256 байт. | ||

| Основные производители: Mitsubishi Electric, Hitachi, Motorola. | |||

| Программирование: метод FN. Стирание: метод FN. | |||

| Примечания: В настоящее время чаще всего используются память с архитектурой NOR и NAND. Hitachi выпускает многоуровневую AND-память с NAND - итерфейсом. Вообще, у существующих сегодня микросхем памяти для ячеек характерно время хранения информации, измеряемое годами и число циклов чтения/записи — от 100 тысяч до нескольких миллионов. Из недостатков, в частности, у флэш-памяти с архитектурой NOR стоит отметить слабую масштабируемость: нельзя уменьшать площадь чипов путем уменьшения размеров транзисторов. Эта ситуация связана со способом организации матрицы ячеек: в NOR архитектуре к каждому транзистору надо подвести индивидуальный контакт. Гораздо лучше в этом плане обстоят дела у флэш-памяти с архитектурой NAND. | |||

Неотъемлемой частью архитектуры является доступ к ячейке памяти.

Существует три основных типа доступа:

· обычный (Conventional) - произвольный асинхронный доступ к ячейкам памяти. Специфика флэш-памяти такова, что сначала нужно удалить старую информацию, а затем уже можно записывать новую. При этом флэш-память содержит только три операции - запись, чтение, стирание. На каждую из операций требуется определенное время. Например, для чтения одного блока затрачивается примерно 60 нс, а для записи 9 мкс. На операцию стирания информации в среднем затрачивается от 0,6 до 4,5 секунды. Это самая долгая операция.

Запись (программирование) флэш-памяти – это замена "1" на "0", а стирание - замена "0" на "1". В качестве "0" и "1" во флэш-памяти используются блоки, которые имеют фиксированные адреса. Каждый блок содержит несколько ячеек, в которых и располагается информация. При записи различной информации количество ячеек постоянно меняется. При стирании информации на модуле флэш-памяти стираются сами блоки. Их стирание влечет за собой удаление всех ячеек, находящихся в блоке.

Для записи и стирания информации применяются специальные программные методы и алгоритмы. Они применяются из-за того, что отдельную ячейку из блока удалить невозможно. Программные алгоритмы помогают осуществить эмуляцию перезаписи байта, используя два параметрических блока размером 8 Кб.

· страничный (Page) - асинхронный, блоками по 4 или 8 слов. Преимущества: очень быстрый произвольный доступ в пределах текущей страницы. Недостаток: относительно медленное переключение между страницами. Иными словами, страничный доступ это режим, который организуется с целью ускорения доступа. Суть его в том, что в пределах выбранной страницы (например 8 байт) доступ может выполняться в ускоренном режиме. Страницей являются 4 или 8 смежных ячеек; первое чтение в странице выполняется со временем доступа порядка 70 нс. Если микросхема остается выбранной, то другие ячейки этой страницы (отличающиеся значением младших битов адреса) можно считывать циклами длительностью порядка 10-20 нс. Понятно, что временные параметры будут отличаться для разных конкретных реализаций памяти, но порядок величин такой.

Доступ к одиночным ячейкам не отличается от обычного типа доступа (Conventional). Естественно, что при этом время доступа к памяти увеличивается. Это происходит из-за необходимости смены начального адреса и переустановки сигналов управления при переходе на другую страницу. В момент снятия управляющих сигналов начинается цикл восстанавливающего чтения, длительностью порядка 300 нс. При этом приостанавливаются дальнейшие обращения к памяти и средний темп доступа снижается.

· пакетный (Burst) - синхронный, данные читаются параллельно, блоками по 16 или 32 слова. Считанные данные передаются последовательно, передача синхронизируется. Преимущество перед обычным типом доступа - быстрое последовательное чтение данных. Недостаток - медленный произвольный доступ.

Микросхемы флэш-памяти с пакетным режимом (Burst Mode) вдобавок к одиночному и страничному режимам (асинхронным) могут работать и в синхронном режиме. Для этого они имеют специальный вход синхронизации CLK. Адрес начала пакета фиксируются по положительному перепаду CLK. Первые данные на выходе появятся через 3 такта, после чего в каждом следующем такте будут выдаваться очередные данные.

| Примечание: В настоящее время выпускаются микросхемы флэш-памяти, позволяющие одновременную запись и стирание (RWW - Read While Write) в разные банки памяти. |

Необходимо отметить, что архитектура флэш-памяти влияет на области ее применения. В самом деле, сфера применения какого-либо типа флэш-памяти зависит в первую очередь от его скоростных показателей и надежности хранения информации. Адресное пространство NOR-памяти позволяет работать с отдельными байтами или словами (2 байта). В NAND-памяти ячейки группируются в небольшие блоки (по аналогии с кластером жесткого диска). Из этого следует, что при последовательном чтении и записи преимущество по скорости будет у NAND. Однако с другой стороны NAND значительно проигрывает в операциях с произвольным доступом и не позволяет напрямую работать с байтами информации.

К примеру, для изменения одного байта требуется:

· Считать в буфер блок информации, в котором он находится.

· В буфере изменить нужный байт.

· Записать блок с измененным байтом обратно.

Следует учесть, так же задержки на выборку блока и на доступ. Поэтому показатели хуже, чем для NOR (но это только для случая побайтовой записи).

В режиме последовательной записи/чтения NAND наоборот показывает более высокие скоростные характеристики. Поэтому, а также из-за возможностей увеличения объема памяти без увеличения размеров микросхемы, NAND нашел применение в качестве хранителя больших объемов информации и для ее переноса.

Что касается NOR - флэш, то чипы с такой организацией используются в качестве хранителей программного кода (BIOS, RAM карманных компьютеров, мобильных устройств и т.п.), иногда реализовываются в виде интегрированных решений (ОЗУ, ПЗУ и процессор на одной мини-плате, а то и в одном чипе). В качестве примера такого использования приведем разработку компании «Gumstix Technology» одноплатный компьютер «Gumstix Verdex Pro ХМ 4» размером с пластинку жвачки. Внешний вид и данные приведены на Рис. 4. Слева внешний вид реальной платы с дух сторон, справа компьютерный чертеж.

| Процессор: Marvell ® PXA270 XScale ™ с. Быстродействие: 400 МГц. | ||||||||||||||||||||||||||||||||||||||||||||||||

| Объем памяти (ОЗУ/флэш): 64 МБ / 16 MB. Разъемы: три разъема (60, 80 и 24 контакта). Операционная система: Linux 2.6.21 или выше. Размеры: 80 mm х 20 mm х 6.3 mm. Вес: 8 граммов. Температурный диапазон: -25 ° C до 85 ° C. Напряжение питания: 3.6V - 5.0V. Рис. 4. Одноплатная ЭВМ «Gumstix Verdex Pro ХМ4» . | ||||||||||||||||||||||||||||||||||||||||||||||||

| Именно NOR-чипы обеспечивают требуемый для таких случаев уровень надежности хранения информации и более гибкие возможности по работе с ней. | ||||||||||||||||||||||||||||||||||||||||||||||||

Суммируя вышесказанное:

· Флэш-память имеет несколько типов организации массива.

· Наибольшее распространение получила память типов И-НЕ (NAND), ИЛИ-НЕ (NOR).

· По архитектуре эти два типа имеют существенные различия.

· Тип ИЛИ-НЕ содержит ячейки, включенные параллельно друг другу и обеспечивает быстрый произвольный доступ к данным, возможность побайтной записи информации. Однако этот тип архитектуры имеет ячейки относительно большого размера, потому плохо масштабируется. Время стирания или записи больше, чем у других типов флэш-памяти.

· Тип И-НЕ содержит ячейки, включенные последовательно (гирляндой), между двумя линиями выборки. Группы ячеек объединяются в страницы. Страницы в блоки. Стоки разных транзисторов такой гирлянды находятся на разных страницах. Поэтому произвольный доступ к ячейкам невозможен. Чтение, запись осуществляются одновременно только в пределах одной страницы, а стирание, осуществляются одновременно только в пределах одного или нескольких блоков. Однако, осуществляется быстрее, чем у типа ИЛИ-НЕ.

· Другие типы архитектуры являются комбинацией этих двух.

Итак, мы рассмотрели принципы действия и устройство ячеек флэш – памяти, способы объединения ячеек и доступа в массивы памяти. Но для практической реализации реальных устройств необходимо создать соответствующие микросхемы, в состав которых входят помимо массивов памяти и другие функциональные элементы, обеспечивающие выполнение целого ряда функций. Перед тем, как перейти к устройству реальных микросхем, рассмотрим организацию структуры данных флэш-памяти, и некоторые особенности ее работы.

Структура блочных (параметрических) данных в микросхеме флэш памяти.

В микросхемах флэш-памяти для более удобной организации данных в блоках разработана особая структура данных, которая представляет собой форму связных списков. Каждая запись, заносимая в этот список, состоит из двух полей. В первое поле заносится значение параметра заносимой записи. Во втором поле указывается адрес для следующей записи этого же параметра. Первое поле обозначается как "Parameter". После "Parameter" стоит номер, например Parameter1. Также в списке имеется ParameterХ, который является переменным указателем, в котором содержится адрес первой записи данного параметра. Если какая-либо ячейка блока содержит значение Parameter1, то в этой ячейке указан адрес первой записи параметра, который содержит первое значение Parameter1 и адрес второй записи Parameter1. Вторая запись, в свою очередь, содержит последнее значение данного параметра и адрес третьей записи. В последней записи, обычно в поле "Next_Record", заносится код, который обозначается как FFh. Он указывает на то, что последующих записей больше нет. Этот код представляет собой значение стертого байта по умолчанию.

Процесс записи информации во флэш-память или какое-либо изменение параметров происходит следующим образом - программа находит первую свободную ячейку в каком-нибудь блоке, новое значение заносится в поле значения новой записи, а чтобы запись была закончена, программа обновляет поле Next_Record. Причем обновление этого поля происходит в предыдущей записи. В результате получается, что каждая последующая запись имеет связь с предыдущей. Такие структуры и особенности записи информации называются связными списками. При чтении данных не нужно просматривать все списки. Программа находит последнее значение данного параметра и по его указателю читает нужные коды.

Ниже приведен пример структуры самого простого связного списка. В данном примере (то же самое относится к любой другой структуре) Parameter_Value является переменным и зависит в большей степени от специфики и объема заносимой информации.

Процесс записи или запоминания информации может происходить до того момента, пока не останется свободного места в модуле флэш-памяти и пока будет допустимо записать полный законченный параметрический блок. При этом в нем должно остаться место для полной записи. После заполнения последнего блока, для того чтобы списки были связными, последнее значение каждого параметра заносится во второй блок. После полного заполнения всего допустимого объема блока флэш-памяти запись последующей информации в него становится невозможной. Для этого следует очистить флэш-память. Очистка модуля флэш-памяти представляет собой стирание одного, нескольких или всех параметрических блоков. При этом процесс стирания происходит за счет поэтапной перезаписи и стирания информации. Например, для того чтобы стереть первый параметрический блок, программе необходимо информацию из него перенести во второй блок, а уже после этого происходит стирание первого. Причем во второй блок переносится не вся информация, содержащаяся в первом блоке, а только действительные значения параметров, относящиеся к последующим блокам. Поскольку стирание флэш-памяти не единственная задача, выполняемая системой, программами для работы с флэш-памятью предусмотрена функция приостановки процесса стирания. Приостановка стирания включается в тех случаях, когда системе необходимо прочитать данные, находящиеся в других параметрических блоках. Команду приостановки стирания дает программа, управляющая модулем флэш-памяти. При выполнении этой программы модуль находится в подвешенном состоянии. Аналогичным примером может послужить "зависание" компьютера при работе. Но в случае с флэш-памятью "зависание" относится только к задаче стирания (и к тому же программа в любую секунду может продолжить эту операцию), а что касается чтения, то для этого нет никаких преград. После того как система прочитает данные, расположенные в других блоках, программа в модуль (микросхему) посылает сигнал о продолжении операции стирания. Стирание параметрического блока будет продолжено с того момента, где оно было прервано. Но пока операция стирания блока не будет полностью закончена, новые данные на его место записать будет невозможно. Все модули флэш-памяти допускают поэтапное (байт за байтом) программирование. Возможно программирование одиночных битов путем маскирования остальных. По организации массива (с точки зрения стирания групп ячеек) различают следующие архитектуры:

Все современные микросхемы секторированы (разбиты на отдельно стираемые блоки), так что остается лишь деление на симметричную и асимметричную архитектуру. В асимметричной архитектуре один из 64-килобайтных блоков разбивается на 8 блоков по 8 Кбайт. Один из блоков имеет дополнительные аппаратные средства защиты от модификации и предназначается для хранения жизненно важных данных, не изменяемых при запланированных модификациях остальных областей. Это предназначено для хранения системного программного обеспечения (BIOS), а привилегированный блок (Boot Block) хранит минимальный загрузчик, позволяющий загрузить (например, с дискеты) и выполнить утилиту программирования основного блока флэш-памяти. Микросхемы могут поддерживать и режим страничной записи (Page Write), в котором они принимают поток байт записи смежных ячеек в страничный буфер на нормальной скорости интерфейса, после чего вся страница записывается в энергонезависимую память. Страничная запись экономит время (запись страницы выполняется за то же время, что и одной ячейки), но размер страничного буфера, как правило, небольшой (4-32 байт для микросхем небольшого объема и до 128-256 байт — большого). Более сложный интерфейс записи использует систему команд, в которую могут входить команды разрешения/запрета стирания и записи, стирание (отдельной ячейки или всей памяти), запись. Микросхема может иметь и специальные внутренние регистры, например регистр состояния, определяющий готовность микросхемы к обмену данными и возможные режимы защиты от модификации ячеек. Стирание во флэш-памяти производится сразу для целой области ячеек (блоками или полностью всей микросхемы). Это позволяет существенно повысить производительность в режиме записи (программирования). Ячейки организованы в матрицу; разрядность данных внешнего интерфейса — 8 или 16 бит (ряд микросхем имеет переключаемую разрядность). Чистые (стертые) ячейки содержат единицу во всех битах; при записи (программировании) нужные биты обнуляются. Возможно последующее программирование и уже записанных ячеек, но при этом можно только обнулять единичные биты, но не наоборот. В единичное состояние ячейки переводятся только при стирании. Стирание выполняется для всей матрицы ячеек; стирание одиночной ячейки невозможно. Чтение флэш-памяти ничем не отличается от чтения любой другой памяти — подается адрес ячейки, и через некоторое время доступа (десятки-сотни нс) на выходе появляются данные. Запись выглядит несколько сложнее — для программирования каждого байта (слова) приходится выполнять процедуру, состоящую из операций записи и считывания, адресованных к микросхеме флэш-памяти. |

Контроллер флэш-памяти.

Очевидно, что помимо собственно матрицы ячеек, в которой хранится информация, флэш-память должна иметь блок отвечающий за управление перезаписью информации. Этим блоком является контроллер флэш-памяти.

Начиная с 90-х годов начался процесс стандартизации флэш-памяти и контроллеры стали размещаться непосредственно в корпусах флэш-памяти. Это позволило решить проблему совместимости флэш - устройств и компьютеров различных производителей, что естественно привело к устойчивому росту спроса на флэш-память.

По мере развития технологий производства микросхем, появилась возможность размещать контроллер и матрицу памяти на одном кристалле, что привело к еще более широкому распространению флэш памяти в разных областях.

Как правило, флэш-память адресуется побитно, побайтно или пословно и может перепрограммироваться. Интегрированный контроллер, управляет процессом стирания и программирования.

Далее, в качестве примера, рассмотрим работу контроллера флэш-памяти семейства MSP430 (Texas Instruments). Данная память является одним из модулей микро – ЭВМ.

Микро-ЭВМ семейства MSP430 содержат 16-разрядное CPU (Central Processing Unit – центральное процессорное устройство – ЦПУ), периферийные модули и гибкую систему тактирования, соединенные через общую адресную шину памяти MAB (Memory Address Bus – адресная шина памяти) и шину памяти данных MDB (Mamory Data Bus – шина данных памяти). Объединяя CPU с отображаемыми в памяти аналоговыми и цифровыми периферийными устройствами, семейство MSP430 реализует приложения со смешанными сигналами, что весьма востребовано в современном физическом эксперименте. Возможность внутрисхемного программирования Flash-памяти позволяет гибко изменять и обновлять программный код, производить регистрацию данных.

Флэш-память в MSP430 адресуется побитно, побайтно или пословно и может перепрограммироваться. Модуль флэш-памяти имеет интегрированный контроллер, управляющий процессом стирания и программирования. Контроллер имеет три управляющих регистра, тактовый генератор и генератор напряжения для обеспечения напряжений стирания и программирования.

Общая блок-схема модуля флэш-памяти с контроллером показана на Рис. 5 .

В разных конкретных реализациях контроллеров флэш-памяти других производителей возможны непринципиальные отличия, но основные блоки, в том или ином виде, присутствуют всегда.

Рис. 5. Блок-схема модуля флэш-памяти.

FCTLx – 16-разрядные регистры (записи/чтения) управления флэш-памятью.

Все режимы работы, все реакции флэш-памяти на те, или иные ситуации определяются содержимым этих регистров. Назначение каждого из них рассмотрено ниже.

Любая операция чтения или записи доступна только при использовании команды-слова управляющих регистров, при этом запись возможна только при наличии в старшем байте пароля записи 0A5h. Любая запись в любой FCTLx регистр с любым значением в старшем байте, отличном от 0A5h вызовет нарушение ключа защиты и запуск системного сброса PUC(Power-up clear – очистка при включении питания). Рассмотрим структуру каждого из регистров и назначение их разрядов.

FCTL1

| FRKEY, читается как 096h FWKEY, должен записываться как 0A5h |

| BLKWRT | WRT | Резерв | Резерв | Резерв | MERAS | ERASE | Резерв |

| FRKEY/FWKEY | Биты 15-8 | Пароль FCTLx. Всегда читается как 096h. Должен записываться как 0A5h, в противном случае будет генерироваться сигнал PUC. | |||||||||||||

| BLKWRT | Бит 7 | Режим блочной записи. Для режима блочной записи также должен быть установлен WRT. Бит BLKWRT автоматически сбрасывается при установке EMEX. «0» Режим блочной записи выключен «1» Режим блочной записи включен | |||||||||||||

| WRT | Бит 6 | Запись. Этот бит используется для выбора любого режима записи. Бит WRT автоматически сбрасывается при установке EMEX. «0» Режим записи выключен, «1» Режим записи включен | |||||||||||||

| Резерв | Биты 5-3 | Зарезервировано. Всегда читается как «0». | |||||||||||||

| MERAS | Бит 2 | Массовое стирание и обычное стирание. Эти биты используются совместно для выбора режима стирания. Биты MERAS и ERASE автоматически сбрасываются, когда устанавливается EMEX. | |||||||||||||

| ERASE | Бит 1 | ||||||||||||||

| |||||||||||||||

| Резерв | Биты 5-3 | Зарезервировано. Всегда читается как 0 | |||||||||||||

FCTL2.

| FWKEYx, читается как 096h должен записываться как 0A5h |

| FSSELx | FNx |

| FWKEY | Биты 15-8 | Пароль FCTLx. Всегда читается как 096h. Должен записываться как 0A5h, в противном случае будет генерироваться сигнал PUC. | |||||

| FSSELx | Биты 7-6 | Выбор источника тактирования контроллера флэш 00 ACLK, 01 MCLK, 10 SMCLK, 11 SMCLK | |||||

| FNx | Биты 5-0 | Делитель тактовой частоты для контроллера флэш. Эти шесть битов позволяют установить необходимый коэффициент деления для тактирования контроллера флэш. Значение коэффициента деления равно FNx+1. К примеру, когда FNx=00h, коэффициент деления равен 1. Когда FNx=02Fh, коэффициент деления равен 64. |

FCTL3.

| FWKEYx, читается как 096h должен записываться как 0A5h |

| Резерв | EMEX | LOCK | WAIT | ACCVIFG | KEYV | BUSY |

| FWKEY | Биты 15-8 | Пароль FCTLx. Всегда читается как 096h. Должен записываться как 0A5h, в противном случае будет генерироваться сигнал PUC. | |||||

| Резерв | Биты 7-6 | Зарезервировано. Всегда читается как «0» | |||||

| EMEX | Бит 5 | Аварийный выход. «0» Нет аварийного выхода, «1» Аварийный выход | |||||

| LOCK | Бит 4 | Блокировка. Этот бит разблокирует флэш-память для выполнения записи или стирания. Бит LOCK может быть установлен в любой момент во время записи байта/слова или операции стирания, при этом выполняемая операция будет нормально завершена. В режиме блочной записи, если бит LOCK устанавливается, когда BLKWRT=WAIT=1, биты BLKWRT и WAIT сбрасываются и режим нормально заканчивается. «0» Разблокировано, «1» Заблокировано | |||||

| WAIT | Бит 3 | Ожидание. Указывает, что происходит запись флэш-памяти. «0» Флэш-память не готова для записи следующего байта/слова. «1» Флэш-память готова для записи следующего байта/слова. | |||||

| ACCVIFG | Бит 2 | Флаг прерывания при нарушении прав доступа «0» Прерывание не ожидается, «1» Ожидание прерывание | |||||

| KEYV | Бит 1 | Ключ нарушения безопасности флэш. Этот бит показывает, что был записан неправильный пароль FCTLx в любой регистр управления флэш-памятью и при его установке генерируется сигнал PUC. Бит KEYV должен быть сброшен программно. «0» Был записан корректный пароль, «1» Был записан некорректный пароль | |||||

| BUSY | Бит 0 | Занято. Бит показывает состояние тактового генератора флэш. «0» Не занят, «1» Занят |

Сегментация флэш-памяти

Флэш-память разбита на сегменты. В неё может быть записан один бит, байт или слово, но сегмент – это минимальный размер флэш-памяти, который можно стереть. Три режима стирания позволяют стереть один сегмент, стереть все главные сегменты или стереть все сегменты (основные и информационные сегменты).

Флэш-память разделена на основной и информационный разделы памяти. Нет никаких различий в работе основного и информационного разделов памяти. Программный код или данные могут быть расположены в любом разделе. Различие между этими двумя разделами заключается в разных размерах сегмента и различных физических адресах.

На Рис. 6 . показана сегментация памяти на основе примера 4 кб флэш-памяти, имеющей восемь основных сегментов и оба информационных сегмента.

Рис. 6 . Сегменты флэш-памяти, пример для 4 кб.