ТЕКСТ ПРОГРАМИ З ПОЯСНЕННЯМ

Вступ

Дана курсова робота виконується з метою більш поглибленого вивчення дисципліни «Мікроконтролери у вимірювальній техніці», набуття навичок самостійного вирішення поставлених задач, більш детального вивчення принципу роботи MCS-51 стенду EV8031, та вдосконалення знань, набутих під час виконання лабораторних робіт.

Для успішного виконання курсової роботи студент повинен вміти працювати з літературою, знати необхідний матеріал, вміти складати алгоритми та розроблювати програми мовою СІ. В курсовій роботі використовуються такі теоретичні відомості, як відомості про принцип роботи, структуру та властивості електронного вольтметра з усередненням, необхідні для кращого розуміння поставленої задачі та розроблення шляхів її реалізації на базі MCS-51 стенду EV8031; відомості про апаратні та програмні можливості використовуваного стенду EV8031 та мікроконтролера MCS-51.

В курсовій роботі використовується програмне середовище Keil uVisioun3.

ТЕОРЕТИЧНА ЧАСТИНА

1.1. Мікроконтролер 8051

1.1.1. Програмна архітектура мікроконтролерів 8051

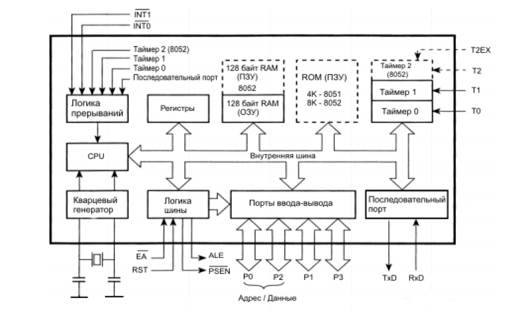

Апаратна архітектура 8051 представлена на рис. 1.1.

Рис. 1.1. Апаратна архітектура 8051

У мікроконтролера 8051 всі обчислення виконуються в арифметико-логічному пристрої, що є частиною базового процесорного модуля (CPU). Обмін даними, що знаходяться в оперативній пам'яті мікроконтролера, а також зчитування команд виконуєся по внутрішній шині 8051. По цій шині здійснюється і обмін даними з портами вводу/виводу P1 - P3, з послідовним портом і таймерами. Внутрішній контролер шини формує необхідні сигнали (EA, ALE, PSEN, RD / WR) для роботи із зовнішньою пам'яттю програм і даних, а також сигнал скидання / початкової установки RST.

Мікроконтролери 8051 розраховані на роботу з системами реального часу, які можуть генерувати певні сигнали, що вимагають негайної реакції мікроконтролера. Для обробки таких сигналів (або подій) служить апаратно реалізована логіка переривань, що дозволяє обробляти сигнали зовнішніх джерел, таймерів і послідовного порту.

Швидкість виконання операцій в системі на базі 8051 залежить від тактової частоти, з якою працює кристал і яка може варіюватися від одиниць до декількох десятків мегагерц. В архітектуру класичного мікроконтролера 8051 були внесені деякі зміни (до двох існуючих таймерів доданий третій, а також розширена внутрішня пам'ять), які привели до створення пристрою 8052, найбільш популярного в даний час.

Мікроконтролера 8051 реалізований у вигляді однокристального пристрою з зовнішніми виводами, позначеними, як показано на рис. 1.2.

Рис. 1.2. Схема розміщення виводів МК 8051

Вхідні і вихідні сигнали мікроконтролера 8051 мають наступні призначення:

• XTAL і XTAL2 -входи підключення кварцового резонатора для роботи генератора тактової частоти мікроконтролера;

• PSEN - сигнал, що використовується при зверненні до зовнішньої пам'яті програм;

• ALE - вихідний сигнал дозволу фіксації адреси при зверненні до зовнішньої пам'яті програм / даних;

• EA - сигнал, що блокує роботу із внутрішньою пам'яттю;

• RST - сигнал загального скидання;

• P0 - P3 - висновки портів введення / виводу мікроконтролера;

• Vss і Vcc - висновки подачі напруги харчування.

Порти P0, P2 і P3 крім функціонування в режимі вводу/виводу дискретних сигналів можуть виконувати, залежно від конфігурації, і інші функції. Так, через порт P0 призверненнях до зовнішньої пам'яті виставляються молодші 8 біт 16-розрядної адреси, а потім, у фазі запису/читання даних, через цей порт йде обмін даними. Порт P2 при зверненнях до зовнішньої пам'яті служить джерелом старших 8 біт 16-розрядної адреси.

Висновки порту P3 мікроконтролера 8051 мають такі альтернативні призначення:

• P3.0 - вхід прийому даних у послідовний порт;

• P3.1 - вихід передачі даних з послідовного порту;

• P3.2 - вхід зовнішнього переривання INT0;

• P3.3 - вхід зовнішнього переривання INT1;

• P3.4 - вхід управління таймером 0;

• P3.5 - вхід управління таймером 1;

• P3.6 - вихід сигналу запису в пам'ять;

• P3.7 - вихід сигналу читання з пам'яті.

Для використання альтернативних функцій порту P3 необхідно налаштувати відповідним чином програмне забезпечення системи 8051.

1.1.2. Структура внутрішньої пам’яті 8051

Мікроконтролера 8051 оперують двома типами пам'яті: пам'яттю програм і пам'яттю даних. Пам'ять даних може бути реалізована як комбінація розміщеного на кристалі (резидентного або on $ chip) статичного ОЗУ і зовнішніх мікросхем пам'яті. Для простих апаратно-програмних конфігурацій із застосуванням 8051 буває досить резидентної пам'яті самого мікроконтролера.

Програмний код розміщується в пам'яті програм, яка фізично може бути реалізована у вигляді одноразово програмованого пристрою (EPROM), перепрограмованого пристрою (EEPROM) або флеш $ пам'яті. Якщо для запису програм використовується EPROM або EEPROM, то програмний код зазвичай розташовується в зовнішньому по відношенню до мікроконтролера пристрої. У переважній більшості сучасних мікроконтролерів 8051 пам'ять програм розташовується у флеш пам'яті, що знаходиться, так само як і резидентна пам'ять даних, на одному кристалі.

Пам'ять програм і пам'ять даних фізично і логічно розділені, мають різні механізми адресації, працюють під управлінням різних сигналів і виконують різні функції.

Пам'ять програм може мати максимальний об'єм, рівний 64 Кб, що зумовлено використанням 16-розрядної шини адреси. У багатьох випадках ємність пам'яті програм, розміщеної на кристалі 8051, обмежена 4, 8 або 16 Кб. У пам'ять програм крім команд можуть записуватися константи, керуючі слова ініціалізації, таблиці перекодування вхідних та вихідних змінних і т.п. Доступ до вмісту пам'яті програм здійснюється за допомогою 16-бітової шини адреси. Сам адреса формується за допомогою якого програмного лічильника (PC), або регістра $ покажчика даних (DPTR). DPTR виконує функції базового регістра при непрямих переходах за програмою або використовується в операціях з таблицями.

Загальна структура пам'яті мікроконтролера 8051 показана на рис. 1.3.

Рис. 1.3. Загальна структура пам'яті мікроконтролера 8051

Розглянемо більш докладно резидентну (on-chip) пам'ять мікроконтролера 8051.Резидентні пам'ять складається з двох частин: внутрішнього ОЗУ розміром 128 байт і пам'яті, що виділяється для регістрівспеціальних функцій (Special Function Registers, SFR). Внутрішнє ОЗУ має структуру,показану на рис. 1.4.

Рис. 1.4. Структура внутрішньої ОЗУ

Для доступу до даних, розміщених у внутрішньому ОЗП, використовується однобайтовий адресу. Архітектура внутрішньої пам'яті даних 8051 дозволяєзвертатися до окремих бітам даних у спеціально виділеної області внутрішнього ОЗУ,починаючи з адреси 0x20 і закінчуючи 0x2F. Таким чином, у зазначеномудіапазоні адрес можна звертатися до 128-бітовим змінним за допомогою командбітових операцій SETB і CLR. Бітові змінні нумеруються, починаючи з 0x0 і закінчуючи0x7F. Це не означає, що не можна звертатися до цих осередків пам'яті, як до байтівпри звичайних операціях з пам'яттю.

У другому випадку звернення виконується до байту за адресою 0x20, а встановлення відповідних бітів виконується операцією «логічне АБО».

У внутрішньому ОЗП мікроконтролера 8051 виділено 4 банки регістрів загального призначення. При включенні мікроконтролера банком за замовчуванням стає банк 0.

При цьому регістру R0 відповідає адреса 0x00, регістру R1 - адреса 0x01, нарешті,регістру R7 при використанні банку 0 відповідає адреса 0x07. Якщо банком за замовчуванням стає, наприклад, банк 1, то регістру R0 буде відповідати адресу0x08, регістру R1 - адреса 0x09 і регістру R7 - адреса 0x0F.

До адресного простору внутрішнього ОЗУ починаючи з адреси 0x80 приєднуються іадреси регістрів спеціальних функцій (рис. 1.5).

Регістри спеціальних функцій (Special Function Registers, SFR) призначені дляуправління ходом обчислювальних операцій, а також відповідають за ініціалізацію, настройку і управління портами вводу / виводу, таймерами, послідовним портом. Крім того, регістри спеціальних функцій містять інформацію про пріоритетипереривань, а також біти управління дозволом переривань. Регістри спеціальнихфункцій із зазначенням їх призначення перераховані в табл. 1.1

Рис. 1.5. регістри спеціальних функцій

Таблиця 1.1. Регістри спеціальних функцій

| Позначення | Опис | Адреса |

| А | Акумулятор | ОЕОН |

| В | Регістр-розширювач акумулятора | OFOH |

| PSW | Слово стану програми | ODOH |

| SP | Регістр-покажчик стека | 81H |

| DPTR | Регістр-покажчик даних (DPH) | 83H |

| (DPL) | 82H | |

| P0 | Порт 0 | 80H |

| P1 | Порт 1 | 90H |

| P2 | Порт 2 | OAOH |

| P3 | Порт 3 | OBOH |

| IP | Регістр пріорітетів переривань | OB8H |

| IE | Регістр маски переривань | OA8H |

| TMOD | Регістр режиму таймера/лічильника | 89H |

| TCON | Регістр управління/статуса таймера | 88H |

| TH0 | Таймер 0 (старший байт) | 8CH |

| TL0 | Таймер 0 (молодший байт) | 8AH |

| TH1 | Таймер 1 (старший байт) | 8DH |

| TL1 | Таймер 1 (молодший байт) | 8BH |

| SCON | Регістр управління прийомопередатчиком | 98H |

| SBUF | Буфер прийомопередатчика | 99H |

| PCON | Регістр управління потужністю | 87H |

Деякі регістри спеціальних функцій допускають побітову адресацію. При цьому звернення до окремих бітам такого регістра можливо як за допомогою звичайних функцій для роботи з байтами, так і за допомогою команд побітових операцій.

Система переривань

Робота мікроконтролера 8051 в системах реального часу була б неможлива без обробки подій, що генеруються зовнішніми пристроями, і установки тимчасових залежностей між подіями в системі. Саме цим цілям і служить логіка обробки переривань 8051, функціональна схема якої показана на рис. 1.15.

Класичний мікроконтролер 8051 має 5 джерел переривань: два зовнішніх переривання, ініційованих сигналами на входах, - INT0 (висновок P3.2) і INT1(висновок P3.3); два переривання таймерів - 0 і 1; переривання послідовного порту(див. рис. 1.6). Очередність виконання двох і більше одночасно надійшли переривань визначається їх пріоритетів.

Рис. 1.6. Структура переривань 8051

Якщо припустити, що всі переривання мають однакові установки пріоритету, то за одночасного виникнення декількох переривань вони обробляються так, як показано на рис. 1.1. Наприклад, переривання INT0 має найвищий пріоритет (йому відповідаєумовне позначення 1 на рис. 1.1), переривання таймера 0 має нижчий пріоритет у порівнянні з INT0 (позначено цифрою 2) і т.д. Найнижчий пріоритет у пристрої 8051 має переривання послідовного порту (позначено цифрою 5 на малюнку). Для мікроконтролера 8052 найнижчим пріоритетом має переривання таймера 2 (позначено цифрою 6). Для зміни пріоритетів виконання переривань слідвстановлювати спеціальні прапори в регістрі пріоритетів IP.

Мікроконтролер реагує на переривання, тільки якщо буде встановлено прапорвідповідного переривання в регістрі TCON.

Будь-яке з переривань буде викликано тільки в тому випадку, якщо його викликвирішено шляхом установки відповідних бітів у регістрі IE.

Розглянемо, як викликаються і обробляються зовнішні переривання INT0 і INT1

в мікроконтролері 8051. Зовнішні переривання INT0 і INT1 можуть бути викликанірівнем або переходом сигналу з 1 в 0 на входах мікроконтролера в залежності від значень керуючих бітів IT0 і IT1 в регістрі TCON. Якщо відповідний біт ITx (x = 0,1)встановлено, то переривання викликається по перепаду 1-0 на відповідному вході INTx мікроконтролера. Якщо ці біти скинуті, то переривання INTx викликається при наявності низького рівня на відповідному вході.

При виникненні зовнішнього переривання INTx встановлюється відповідний прапор IEx в регістрі TCON, який ініціює виклик відповідної підпрограми обслуговування або,по-іншому, програми обробника переривання. Скидання прапора IEx виконується апаратно у випадку, якщо переривання було викликано перепадом сигналу на вході INTx. Якщо ж вхід переривання INTx налаштований на спрацювання за низьким рівнем, то про стан прапора IEx повинна піклуватися програма $ обробник даного переривання.

Зовнішні переривання INT0 і INT1 можуть (якщо дозволені) викликатися одним з трьох способів:

· установкою низького рівня сигналу на відповідному виводі мікроконтролера;

· програмної установкою бітів P3.2 та / або P3.3;

· установкою прапора переривання IE0 або IE1.

Переривання від таймерів викликаються при переповненні регістрів таймера (TH0 - TL0 для таймера 0, TH1 - TL1 для таймера 1 і TH2 - TL2 для таймера 2). Для всіх трьох таймерів при досягненні значень 0xFF в THx - TLx (x = 1, 2, 3) наступний інкремент таймера викличе установку прапора TFx, що ініціює переривання. Прапори переривання таймерів 0 і 1 розміщені в регістрі TCON, при цьому TF0 відповідає біту TCON.5, а TF1 - биту TCON.7.

Прапори запитів переривання від таймерів TF0 і TF1 скидаються автоматично при передачі управління підпрограмі обслуговування.

Переривання послідовного порту викликається установкою одного з прапорів - TI або RI (див. рис. 1.1). Прапори запитів переривання RI і TI встановлюються логікою послідовного порту апаратно, але скидатися повинні програмою. Переривання можуть бути викликані або скасовані програмою, тому що всі перераховані прапори програмно доступні. Обмін даними через послідовний порт буде розглянуто далі в цій книзі, тому зупинятися більш докладно на особливостях обробки переривань послідовного порту ми поки не будемо.

Всі операції з обробки переривань виконує логіка переривань мікроконтролера. Прапори переривань опитуються в кожному машинному циклі, при цьому аналіз пріоритетів переривань виконується протягом наступного машинного циклу. Логіка переривань апаратно сформує дальній виклик LCALL відповідної програми $ обробника переривання, якщо тільки цей виклик не блокується з однієї з таких причин:

• в даний момент обслуговується запит переривання з пріоритетом рівним або

більш високим, ніж поточний;

• поточний машинний цикл не є останнім у циклі виконуваної команди;

• в даний момент виконується команда RETI або будь-яка команда, яка звертається до одного з регістрів - IE або IP.

Якщо прапор переривання був встановлений, але по кожній з перерахованих причин переривання не було обслуговано, а прапор до моменту закінчення блокування був скинутий, то запит переривання втрачається.

Паралельні порти вводу / виводу даних мікроконтролера 8051 має чотири 8-бітових порту введення / виводу, позначених P0- P3 і призначених для введення або виведення інформації як у формі байта, так і побитово.

Кожен порт містить керований регістр-клямку, вхідний буфер і вихідний драйвер. Узагальнена функціональна схема порту введення / виводу показана на рис. 1.7.

Рис. 1.7. Узагальнена функціональна схема порту введення / виводу

Порт P0 є двонаправленим, а порти P1 - P3 - квазідвунаправлення, при цьому кожна лінія портів може бути використана незалежно від інших для введення або виведення. По сигналу скидання в регістри-засувки всіх портів автоматично записуються одиниці, що переводить вихідні лінії портів в режим введення. Всі порти можуть бути використані для організації введення / виводу інформації з двонаправленим лініях передачі.

Однак порти P0 і P2 не можуть бути використані для цієї мети у випадку, якщо система має зовнішню пам'ять, зв'язок з якою організовується через загальну поділювану шину адреси / даних, що працює в режимі тимчасового мультиплексування. Схема функціонування однієї лінії введення / виводу порту P0 показана на рис. 1.8.

Рис. 1.8. Схема функціонування однієї лінії введення / виводу порту P0

Вихідні драйвери порту P0 реалізовані з відкритим стоком, як це видно з рис. 1.12,тому напряму використовувати цей порт для введення / виведення даних не можна. Для роботи порту P0 в режимі введення / виведення даних потрібно до виводів порту приєднати резистори номіналом 10 К (рис. 1.9).

Рис. 1.9. Використання ліній Р0 для вводу/виводу

Для читання порту P0 потрібно спочатку записати в нього одиниці, а потім прочитати вхідне значення. Апаратна архітектура портів P1 - P3 дещо відрізняється від тієї, що реалізована дляP0. Функціональна схема однієї лінії введення / виводу портів P1 - P3 показана на рис.1.10.

Рис. 1.10. Функціональна схема однієї лінії введення / виводу портів P1 - P3

Вихідні каскади портів P1 - P3 використовують внутрішні підтягують резистори, з'єднані зі стоком вихідних транзисторів, тому необхідність у зовнішніх резисторах, як у випадку порту P0, відпадає. Вихідні драйвери портів 0 і 2, а також вхідний буфер порту 0 використовуються при зверненні до зовнішньої пам'яті. При цьому через порт 0 в режимі тимчасового мультиплексування спочатку виводиться молодший байт адреси, а потім видається або приймається байт даних. Через порт 2 виводиться старший байт адреси в тих випадках, коли розрядність адреси дорівнює 16 біт.

Порти P1, P2 і P3 можуть використовуватися, так само як і порт P0, для введення/виведення даних, при цьому не потрібно встановлювати підтягують резистори, як це робиться для порту P0. Як і для порту P0, при читанні даних слід записати у відповідні розряди портів P1, P2 і P3 одиниці.

Усі висновки порту P3 можуть бути використані для реалізації альтернативних функцій. Ці функції можуть бути задіяні шляхом запису одиниці у відповідні біти регістра-засувки (P3.0 - P3.7) порту P3.

Звернення до портів введення / виведення можливо з використанням команд, що оперують з байтом, окремим бітом або з довільною комбінацією бітів. При цьому в тих випадках, коли порт є одночасно і операндом і місцем призначення результату, пристрій управління автоматично реалізує спеціальний режим, який називається «читання-модифікація-запис». Цей режим обігу передбачає введення сигналів не з зовнішніх висновків порту, а з його регістра $ засувки, що дозволяє виключити неправильне зчитування раніше виведеної інформації. Цей механізм звернення до портів реалізований в командах:

• ANL - «логічне І», наприклад: ANL P1, А;

• ORL - «логічне АБО», наприклад: ORL P2, А;

• XRL - «виключає АБО», наприклад: XRL Р3, А;

• JBC - перехід з подальшим очищенням біта, наприклад: JBC P1.1, LABEL;

• CPL - інверсія бита, наприклад: CPL Р3.3;

• INC - інкремент порту, наприклад: INC P2;

• DEC - декремент порту, наприклад: DEC P2;

• DJNZ - декремент порту і перехід, наприклад: DJNZ P1, LABEL;

• MOV PX.Y, C - передача біта перенесення C в біт Y порту X;

• SET PX.Y - установка біта Y порту X;

• CLR PX.Y - скидання біта Y порту X.

При роботі з портами введення / виводу мікроконтролера 8051 необхідно враховувати, що вихідні драйвери цих портів можуть забезпечити максимальний струм в навантаженні порядку декількох міліампер, тому при підключенні потужнострумових вихідних навантажень слід використовувати буферні схеми.

Вольтметри

1.2.1 КЛАСИФІКАЦІЯ ВОЛЬТМЕТРІВ

Електронні вольтметри діляться на аналогові і дискретні. В аналогових вольтметрах вимірювана напруга перетворюється в пропорційне значення постійного струму, що вимірюється магнітоелектричним мікроамперметром, шкала якого градуюється в одиницях напруги. В дискретних вольтметрах вимірювана напруга піддається ряду перетворень, в результаті яких аналогова вимірювана величина перетворюється в дискретний сигнал, значення якого відображується на індикаторному пристрої у вигляді цифр.

По роду струму електронні вольтметри діляться на:

· Вольтметри постійної напруги;

· Вольтметри змінної напруги;

· Універсальні вольтметри;

· Імпульсні вольтметри,

крім того є вольтметри з частотно-вибірковими властивостями – селективні.

При розробці електронних вольтметрів враховуються наступні технічні вимоги:

· Висока чутливість;

· Широкі границі вимірюваної напруги;

· Широкий діапазон робочих частот;

· Великий вхідний опір і мала вхідна ємність;

· Мала похибка;

· Відома залежність показів від форми кривої вимірюваної напруги.

Перераховані вимоги неможливо задовольнити в одному приладі, тому випускаються вольтметри з різними структурними схемами.

1.2.2 ЦИФРОВІ ВОЛЬТМЕТРИ

Принцип роботи вольтметрів дискретної дії полягає в перетворенні вимірюваного постійної або повільно змінної напруги в електричний код, який відображується на табло в цифровій формі. У відповідності до цього узагальнена структурна схема цифрового вольтметра (рис 1.11) складається з вхідного пристрою ВхП, аналого-цифрового перетворювача АЦП і цифрового індикатора ЦІ.

Рис. 1.11 – узагальнена структурна схема цифрового вольтметра

Вхідний пристрій призначений для зміни масштабу вимірюваної напруги, фільтрації завад і, при вимірюванні змінної напруги, - для її перетворення в постійну. Відповідно до призначення у вхідному пристрої мається атенюатор (дільник напруги), підсилювач, фільтр нижніх частот і перемикач полярності. В вольтметрах змінної напруги передбачається перетворювач, зазвичай середньо випрямленого значення.

Схемні рішення цифрових вольтметрів визначаються видом аналого-цифрового перетворювача.

1.2.3 ВОЛЬТМЕТРИ СЕРЕДНІХ ЗНАЧЕНЬ

1.2.4

Активні перетворювачі середніх значень мають кращі характеристики по чутливості і динамічному діапазоні, чим пасивні. По способу лінеаризації характеристики перетворення їх можна підрозділити на перетворювачі:

1. Із застосуванням негативного зворотного зв'язку (НЗЗ);

2. Реалізуючі метод взаємозворотніх характеристик з керованими випрямлячами.

Перетворювачі з застосуванням НЗЗ. Вихідний опір підсилювача, у ланцюг зворотного зв'язку якого включені випрямні елементи, збільшується в  раз. Внаслідок цього вихідна напруга перетворювача, що знімається з навантаження, включеної послідовно з випрямним елементом, мало залежить від нелінійності останнього, тому що підсилювач працює в режимі генератора струму. Точність перетворювача визначається в основному нестабільністю і нелінійністю зворотних опорів діодів. Схема найпростішого перетворювача середніх значень з НЗЗ показана на рис. 1.12

раз. Внаслідок цього вихідна напруга перетворювача, що знімається з навантаження, включеної послідовно з випрямним елементом, мало залежить від нелінійності останнього, тому що підсилювач працює в режимі генератора струму. Точність перетворювача визначається в основному нестабільністю і нелінійністю зворотних опорів діодів. Схема найпростішого перетворювача середніх значень з НЗЗ показана на рис. 1.12

Рис 1.12 – Схема найпростішого перетворювача середніх значень з НЗЗ

Так, як діод V1 включений у прямий канал пристрою, то при великих значеннях коефіцієнта підсилення функція перетворення залежить від стабільності резисторів R1, R2 і R3. Однак граничну точність такої схеми одержати важко внаслідок нелінійності і нестабільності вольт-амперної характеристики діода V2, через який замикається ланцюг НЗЗ для позитивної напівхвилі u(t). Дійсно, при подачі на вхід негативної напівхвилі напруга на вході ФНЧ

,

,

де – зворотний опір діода V2. З даного вираження випливає, що в загальному випадку функція перетворення залежить ще і від .Його вплив тим менше, чим більше величина опору в порівнянні з опорами інших елементів перетворювача. У межах u1(t) прагне до  .

.

З ростом частоти коефіцієнт підсилення підсилювача падає, а отже, і зменшується глибина зворотного зв'язку. Це знижує лінійність характеристики перетворення на високих частотах, особливо при низьких рівнях вхідної напруги.

Для зменшення пульсацій вихідної напруги застосовують схему двонапівперіодного перетворювача. У схемі на рис.1.13вихідні напруги однонапівперіодних випрямлячів сумуються на вході диференціального підсилювача П1. При позитивній напівхвилі вхідного сигналу діод V1 замкнений, діод V2 відкритий, напруга в точці А дорівнює напрузі на вході.

Рис. 1.13 – Схема двонапівперіодного перетворювача

.

Для забезпечення рівності коефіцієнтів передачі при позитивній і негативній полярностях вхідної напруги необхідно виконати умову:

.

.

В даному випрямлячі максимальна вхідна напруга обмежена припустимим значенням синфазної напруги операційних підсилювачів V1,V2. Вихідний опір випрямляча визначається вихідним опором V2, охопленого НЗЗ. Тому, що вихідний опір однонапівперіодного випрямляча приймає значення 0 чи R2 в залежності від полярності вхідного сигналу, то виникає модуляція вхідного струму V2. Тому при побудові прецизійного випрямляча необхідно вибирати V2 з мінімальним вхідним струмом.

Якщо паралельно R2 включити конденсатор С, то на виході V2 буде постійна напруга, пропорційне средньовипрямленому значенню вхідної напруги.

Рис.1.14 – Структурна схема вольтметра середніх значень

1.3 Цифрові пристрої розгортуючого зрівноваження

1.3.1 АЦП РОЗГОРТУЮЧОГО ЗРІВНОВАЖЕННЯ

Цифрові перетворювачі розгортуючого зрівноваження працюють циклічно. У кожному циклі за лінійно-ступінчастим законом змінюється компенсуюча напруга від нуля до номінального значення, і перетворювач щоразу заново вимірює повне значення вхідної напруги Ux (рис. 1.15).

Рис. 1.15 – Графік роботи цифрового перетворювача розгортуючого зрівноваження

Рівняння перетворення без урахування похибок визначається за формулою

,

,

де Nk – номер ступеня, для якого виконується умова компенсації;

Uк – напруга ступеня квантування;

– номінальна напруга перетворювача;

– номінальна напруга перетворювача;

Nн – номінальне (максимальне) значення коду.

Результат вимірювання відносять до початку або до кінця циклу, тобто до моментів часу, відокремлених інтервалами  . Якщо кожний результат вимірювання реєструється, то для відомого порядкового номера

. Якщо кожний результат вимірювання реєструється, то для відомого порядкового номера  даного результату вимірювання можна визначити відповідний момент його отримання, рівний

даного результату вимірювання можна визначити відповідний момент його отримання, рівний  . Таким чином, час обробки результату вимірювання для даного типу перетворювачів сталий і дорівнює

. Таким чином, час обробки результату вимірювання для даного типу перетворювачів сталий і дорівнює

,

,

де  – час відпрацювання одного ступеня квантування.

– час відпрацювання одного ступеня квантування.

Перетворювачі розгортуючого зрівноваження можуть працювати і в режимі зі змінною тривалістю циклу, коли зміна компенсуючої напруги припиняється в момент компенсації напруг, тобто коли  =

=  . У цьому разі маємо вищу швидкодію, але для визначення моменту часу, якому відповідає виміряне значення вхідної величини, схему перетворювача потрібно доповнювати вимірювачем часових інтервалів, що призводить до її ускладнення.

. У цьому разі маємо вищу швидкодію, але для визначення моменту часу, якому відповідає виміряне значення вхідної величини, схему перетворювача потрібно доповнювати вимірювачем часових інтервалів, що призводить до її ускладнення.

Аналого-цифрові перетворювачі (АЦП) застосовуються у вимірювальних системах і вимірювально-обчислювальних комплексах для узгодження аналогових джерел вимірюваних сигналів з цифровими пристроями обробки і представлення результатів вимірювання. Існують різні методи побудови АЦП. Вони відрізняються за складністю реалізації, завадостійкості, швидкодії.

У системах де основним критерієм є швидкодія застосовують АЦП паралельного перетворення. Але АЦП цього типу досить складні в реалізації. Для n-розрядного АЦП необхідно 2n-1 компараторів і паралельний дільник напруги, який виробляє 2n-1 рівнів квантування.

Для реалізації систем з високою завадостійкістю застосовують інтегруючі АЦП. Такий АЦП складається з двох перетворювачів. Вимірюється напруга перетворюється у тривалість імпульсу, а потім тривалість імпульсу перетворюється в цифровий код. Одним з найпоширеніших є АЦП, побудований на цифро-аналоговому (ЦАП) перетворювачі. Схема цього АЦП наведена на рисунку 1.16

Рис. 1.16 – Схема АЦП побудованого на ЦАП

Код формується лічильником, при організації жорсткої логіки, або програмно, якщо АЦП працює в складі обчислювального комплексу. Вхідний код перетворюється в аналоговий сигнал за допомогою ЦАП. Напруга з виходу ЦАП надходить на один з входів компаратора. На інший вхід подається вимірювана напруга Ux. У момент, коли напруга ЦАП дорівнюватиме вимірюваному, компаратор формує сигнал 'Stop' який свідчить про закінчення циклу виміру. При формуванні коду використовуються різні алгоритми. Найпростішим алгоритмом є порозрядне зрівноваження. При такому підході код змінюється від мінімального шляхом збільшення одиниці молодшого розряду до тих пір, поки напруга ЦАП не зрівняється з вимірюваним напругою. Недоліком порозрядного врівноваження є маленька швидкодія.

Для скорочення часу перетворення застосовується метод половинних наближень. Зрівноважування починається зі старшого розряду. У цьому розряді встановлюється одиниця і читається стан компаратора. Якщо напруга ЦАП більше вимірюваного то розряд скидається, а якщо менше, то розряд зберігає свій стан. Далі таким же чином обробляється наступний розряд. Перетворення закінчується тоді, коли будуть опрацьовані всі розряди.

У системах стеження за певними параметрами часто необхідно безперервно зчитувати стан датчика. Це забезпечується малим часом перетворення за рахунок застосування стежить АЦП. Суть даного алгоритму полягає в тому, що спочатку код формується методом половинних наближень. А після порівняння з вимірюваним напругою АЦП відстежує зміну напруги. Якщо напруга зростає то код порозрядно збільшується до тих пір, поки напруга ЦАП не зрівняється з вимірюваним, і навпаки. У стенді АЦП побудований на мікросхемах AD7801 (восьмирозрядний ЦАП) і LM358 (ОУ в якості компаратора) (Рис 1.17). Стан компаратора можна вважати з виводу порту Р1.7 однокристальної ЕОМ, про закінчення циклу перетворення також свідчить свічення світлодіода підключеного до виходу компаратора. Доступ до ЦАП здійснюється як до осередку зовнішнього ОЗУ за адресою 0x8000h для восьми розрядів і 0x8002h для ще двох додаткових старших розрядів.

Вимірювана напруга Ux формується змінним резистором (якщо встановлена перемичка J5), або джерело сигналу підключається до клемника.

Рис. 1.17 – Схема приблизного розташування та підключення ЦАПа та компаратора у мікроконтролері МС-8051

1.3.2 ЦИФРОВІ ВОЛЬТМИТРИ РОЗГОРТУЮЧОГО ЗРІВНОВАЖЕННЯ

Цифрові прилади з рівномірно-ступінчатою зміною Uk побудовані за комбінованою структурною схемою і складаються з двох частин: розгортаючогося перетворювача вимірюваної напруги Ux в проміжний число-імпульсний код N(1) і СТ. На протязі кожного циклу СТ перетворює кількість імпульсів N(1) у цифровий десятковий код, зручний для керування цифровим відліковим пристроєм.

Спрощена структурна схема цифрового вольтметра даного типу (рис. 1.18) складається х підсилювача некомпенсації, ключа, генератора імпульсів, СТ і перетворювача одиничного коду в рівномірно-ступінчату напругу ПКН. В якості ПКН в даному випадку використовується генератор рівномірно-ступінчатої напруги. При включенні приладу в режим разових вимірювань в момент відкривається ключ SW, і імпульси від генератора надходять на лічильник і на ПКН. З надходженням кожного імпульсу напруга на виході ПКН зростає на одну ступінь Uk. В момент t1 рівності Uk= Ux= U1 УН закриває ключ SW, імпульси на лічильник і ПКН не надходять і вимірювання закінчується.

Якщо всі ступені qu напруги uk рівні між собою, то N1=u1/qu

Рис. 1.18 – Структура цифрового вольтметра розгортуючого зрівноваження .

1.3.3 ПОХИБКИ ЦИФРОВИХ ПРИСТРОЇВ РОЗГОРТУЮЧОГО ЗРІВНОВАЖЕННЯ

Статистичні похибки

До статистичних похибок відносяться наступні: похибки від квантування по значенню к, від порога чутливості п і похибки компенсуючої величини. Похибки компенсуючої величини, що виникають в аналогових зворотніх перетворювачах і перетворювачах код-аналог, і похибка п приладів розгортуючого зрівноваження з лінійною зміною.

Розглянемо похибку від квагтування. В цифрових циклічних приладах вихідний код N наближається до шуканого відліку Nx з одного боку, зверху або знизу, тому при Хп.ч=0 максимальна абсолютна похибка від квантування дорівнює ступені qx. Наприклад, у приладах з рівномірно-ступінчатою зміною xk при всіх значеннях Х від 99 до 100 число ступенів квантування хk, або відлік Nx, буде дорівнювати 99. Відповідно, максимальна абсолютна похибка від квантування буде дорівнювати одиниці. Наведена похибка від квантування

к= qx/xн100=100/ Nн. Для зменшення похибки від квантування в компенсуючи величину хк постійну складову, рівну 1/2qx тобто, збільшують значення у порівнянні із Nqx на 1/2qx. Наприклад, цифровому відліку N=98 буде відповідати xk=98qx+qx/2. Якщо значення Х буде в межах від 97,5qx до 98,5qx, то цифровий відлік в цьому випадку буде дорівнювати Nk=98. В даному випадку похибка від квантування становитиме qx/2.

Практична частина

2.1 АЛГОРИТМ ПРОГРАМИ ДЛЯ РЕАЛІЗАЦІЇ ЕЛЕКТРОННОГО ВОЛЬТМЕТРА З УСЕРЕДНЕННЯМ

Підпрограма переривання від INT0

Підпрограма переривання від INT1

Підпрограма виводу vivod

Основна програма

ТЕКСТ ПРОГРАМИ З ПОЯСНЕННЯМ

| #include<reg51.h> | Обов’язкове підключення спеціального регістру для Keil |

| unsigned char xdata *DAC_LO=0x8000; | Надання змінній DAC_LO значення 8000- адреси для відправлення молодших бітів ЦАПу |

| unsigned char xdata *DAC_HI=0x8002; | Надання змінній DAC_HI значення 8002- адреси для відправлення старших бітів ЦАПу |

| unsigned char xdata *PRT=0x8003; | Надання змінній PRT значення 8003- адреси для надсилання сигналу включення додаткової плати |

| unsigned char xdata *HI=0xA000; | Надання змінній HI значення A000- адреси лівої пари статичних індикаторів |

| unsigned char xdata *LI=0xB000; | Надання змінній LI значення В000- адреси правої пари статичних індикаторів |

| unsigned int mode,min,max,s3,m3,s2,m2,s1,m1; | Об’явлення змінних (глобальних) |

| sbit p=P1^7; | Присвоєння змінній р значення ноги 7 порту Р1 мікроконтролера |

| void moda() interrupt 1 using 1 { | Підпрограма переривання від INT0, з назвою moda, користуємося першим банком регістрів |

| If (mode<3) { | Перевіряємо значення mode |

| mode++; } | Збільшення значення mode на одиницю |

| else { | Якщо значення mode>3, виконуємо наступні дії |

| mode=0; }} | Занулення змінної mode |

| void nol() interrupt 2 using 1 { | Підпрограма переривання від INT1, з назвою nol, користуємося першим банком регістрів |

| max=0; | Занулення змінної max, для порівняння з поточним значенням (чи більше max) |

| min=0xFFFF; } | Надання змінній min значення FFFF, для порівняння з поточним (чи менше min) |

| void vivod(unsigned int x) { | Підпрограма – функція від х |

| s3=x/1000; | Блок операцій, що перетворює значення х так, щоб на індикаторі воно відображалось за допомогою шістнадцяткового коду у десятковій системі |

| m3=x%1000; | |

| s2=m3/100; | |

| m2=m3%100; | |

| s1=m2/10; | |

| m1=m2%10; | |

| x=(s3<<12)+(s2<<8)+(s1<<4)+m1; | |

| *LI=x&0x00FF; | Виведення на екран перших восьми розрядів числа х |

| *HI=(x&FF00)>>8; } | Виведення на екран 9-го і 10-го розрядів числа х |

| void main() { | Початок основної програми |

| unsigned int i,j,sum,Res,k; | Об’явлення змінних |

| IE=0x85; | Запрограмовуємо регістр IE (дозволяємо переривання від INT1 i INT0) |

| TCON=0x5; | Запрограмовуємо регістр TCON (обираємо режим роботи переривань, по задньому фронту) |

| *PRT=0x80; | Підключення плати розширення |

| while(1) { | Нескінчений цикл для постійного виконання усієї програми |

| for (i=0;i<1024;i++) { | Початок циклу із лічильником і, що іде від 0 до 1024 максимум |

| *DAC_LO=i&0xFF; | Відправка на ЦАП перших 8-ми розрядів числа і (проводиться логічна операція І («множення») із маскою «1111 1111) |

| *DAC_HI=(i&0x300)>>8; | Відправка на ЦАП 9-го і 10-горозрядів числа і («множення» із маскою «11 0000 0000») |

| for(j=0;j<1;j++) {} | Порожній цикл на один «оберт», що дає час ЦАПу в цілому, та компаратору зокрема зреагувати на вхідні дані |

| if (p==0) { | Умовний перехід (програма всередині виконується лише за умови, якщо біт р прийняв значення 0, а отже рівень тієї напруги, що ми подавали на ЦАП перевищив рівень вимірюваної напруги) |

| if (k<=20) { | Перевіряємо значення k |

| sum=sum+i; | Додаємо до змінної sum, значення числа і, отримане значення присвоюємо змінній sum |

| k=k+1; } | Додаємо до k одиницю і отримане значення присвоюємо k |

| else { | Якщо k>22, виконуємо наступні дії |

| Res=sum/20; | Ділимо значення sum на 22(кількість усереднень) і отримане значення присвоюємо змінній Res |

| k=0; | Занулення змінної k |

| sum=0; } | Занулення змінної sum |

| if (Res<min) { | Перевіряємо значення Res, чи менше воно за мінімальне |

| min=Res; } | Присвоюємо мінімальному значення Res |

| if (Res>max) { | Перевіряємо значення Res, чи більше воно за максимальне |

| max=Res; } | Присвоюємо максимальному значення Res |

| for (j=0;j<100;j++) {} | Порожній цикл на сто «обертів» для більшої затримки значень на екранах, тобто для зменшення «мерехтіння» |

| i=0; | Занулення змінної і |

| Switch (mode) { | Перемикач, який залежить від значення змінної mode |

| case 0: { | Ключове слово, що вказує на те, що якщо змінна mode набула значення 0, то виконуються дії у дужках |

| vivod (Res); | Виклик функції виводу результату Res |

| break; } | Вихід з case |

| case 1: { | Ключове слово, що вказує на те, що якщо змінна mode набула значення 1, то виконуються дії у дужках |

| vivod (min); | Виклик функції виводу результату min |

| break; } | Вихід з case |

| case 2: { | Ключове слово, що вказує на те, що якщо змінна mode набула значення 2, то виконуються дії у дужках |

| vivod (max); | Виклик функції виводу результату max |

| break; } | Вихід з case |

| default: { | Ключове слово, що вказує на те, що якщо змінна mode набула значення відмінного від 0,1,2, то виконуються дії у дужках |

| vivod (Res); | Виклик функції виводу результату Res |

| break; } } | Вихід з default |

| }}}} | Закінчення всіх циклів і основної програми |

ВИСНОВКИ

Під час виконання курсового проекту ми детальніше ознайомились з будовою, функціями, властивостями, організацією пам’яті, системою переривань та принципами роботи мікроконтролера 8051, набули навичок розроблення програм мовою СІ, що реалізують поставлену задачу, а саме вимірювач частоти, застосували алгоритми усереднення та представлення результату у двійково-десятковому коді, навчилися самостійно складати алгоритми і тексти програм для їх дослідження в середовищі Keil uVisioun3.

В результаті поставлена задача виконана: за допомогою MCS-51 стенду EV8031 ми змогли побачити виведення результату вимірювання напруги у вольтах з 20-кратним усередненням, а саме її мінімального, максимального та поточного значення при натисненні кнопки переривання INT1, та зупинку та перезапуск програми при надходженні переривання від кнопки INT0. Нажаль, програмно розробити ідеальний вольтметр середніх значень не вдалось, так як мікроконтролеру потрібен час для виконання операцій, які не стосуються безпосередньо процесу вимірювання (усереднення, пошук максимального та мінімального значень та ін.)

Курсова робота складається з 28 сторінок, містить: Вступ, Теоретичну частину , Практичну частину та Висновок; 17 рисунків, алгоритми розроблюваної програми та підпрограм обробки переривань та текст отриманої програми.