Технологии электронных схем

Основой электронных технологий в настоящее время являются полупроводники (semiconductors) — вещества, электропроводность которых увеличивается с ростом температуры и является промежуточной между проводимостью металлов и изоляторов.

Наиболее часто используемыми в электронике полупроводниками являются кремний и германий.На их основе путем внедрения примесей в определенных точках кристаллов создаются разнообразные полупроводниковые элементы, к которым, в первую очередь, относятся:

• проводники, коммутирующие активные элементы;

• вентили, выполняющие логические операции;

• транзисторы (полупроводниковые триоды), предназначенные для усиления, генерирования и преобразования электрического тока;

• резисторы, обеспечивающие режимы работы активных элементов;

• приборы с зарядовой связью (ПЗС), предназначенные для кратковременного хранения электрического заряда и используемые в светочувствительных матрицах видеокамер;

• диоды и др.

В настоящее время используется несколько технологий построения логических элементов:

• транзисторно-транзисторная логика (ТТЛ, TTL);

• логика на основе комплементарных МОП-транзисторов (КМОП, CMOS);

• логика на основе сочетания комплементарных МОП- и биполярных транзисторов (BiCMOS).

Кроме того, различают:

• положительную логику, или систему высоких потенциалов;

• отрицательную логику, или систему низких потенциалов;

• смешанную.

При положительной логике напряжение высокого уровня соответствует логической «1», а при отрицательной логике — «О».

Логические элементы, функционирующие в системе высоких потенциалов, дуальны элементам, работающим в системе низких потенциалов. Например, в системе высоких потенциалов элемент реализует функцию «ИЛИ-HE», а в системе низких потенциалов — «И-НЕ».

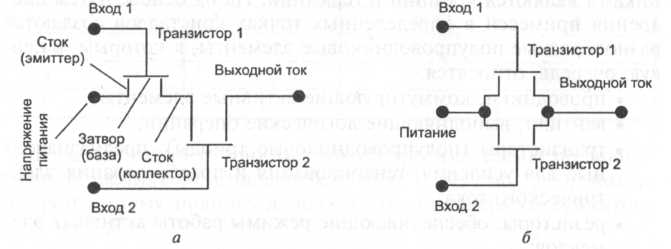

Рассмотрим рис. 1.16, на котором достаточно упрощенно представлены транзисторные сборки «И» (последовательно включенные транзисторы) и «ИЛИ» (параллельное включение). Входные и выходные сигналы «1» представляются высоким уровнем напряжения на коллекторе транзистора (практически равным напряжению питания). Сигналу «О», наоборот, соответствует низкий уровень выходного напряжения.

Рис. 1.16. Пример реализации сборок «И» (о) и «ИЛИ» (б)

Поскольку, например, в большинстве современных персональных компьютеров напряжение питания составляет 3,3 В (в более ранних версиях, до Pentium — 5 В), то выходная «1» задается напряжением 3,3 В.

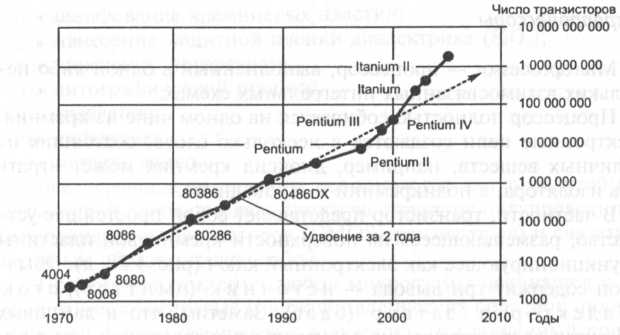

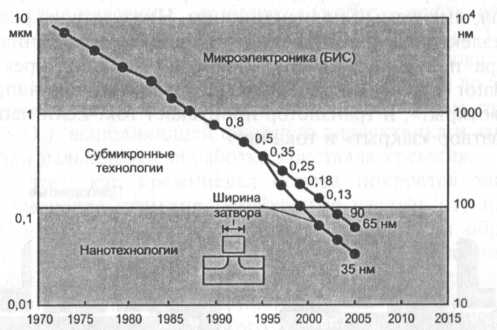

На рис. 1.17 приводится иллюстрация так называемого «закона/правила Мура», с высокой точностью демонстрирующего удвоение за 18—24 мес. количества транзисторов в процессорах. Основой этой закономерности является объективный процесс увеличения плотности упаковки элементов микросхем (рис. 1.18).

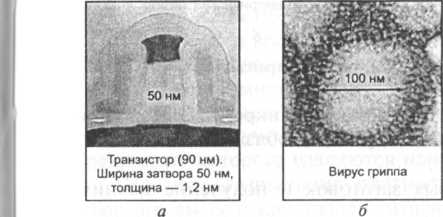

Ключевыми выражениями при описании микросхемных элементов (рис. 1.18) являются такие, как «технология 130 нм», «технологический процесс 0,5 мкм» и т. д. Это означает, что размеры транзисторов или других элементов соответственно не превышают 130 нанометров (1 нм = 10~9 м) либо же 0,5 микрон (1 мкм = 10'6 м) — рис. 1.19.

В процессоре Intel 4004 (1971 г.) использовалась технология 10мкм] в процессоре Pentium II (1998 г.) — технология 0,25мкм\ в процессорах Intel Pentium IV Prescott и AMD Athlon 64 Toledo (2004 г.) — нанотехнологии 0,09 мкм (90 нм) (см. также табл. 3.3 и 3.6).

Рис. 1.17. Правило Мура (количество транзисторов в интегральной схеме удваивается каждые 18 мес.)

Рис. 1.18. Динамика изменений размеров схемных элементов

Рис. 1.19. Нанотехнологии наглядно: а — транзистор (90 нм); б — вирус гриппа (100 нм)

Микропроцессоры

Microprocessor — процессор, выполненный в одной либо нескольких взаимосвязанных интегральных схемах.

Процессор полностью собирается на одном чипе из кремния. Электронные цепи создаются в несколько слоев, состоящих из различных веществ, например, диоксид кремния может играть роль изолятора, а поликремний — проводника.

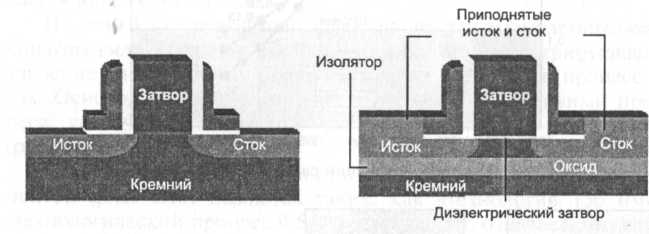

В частности, транзистор представляет собой простейшее устройство, размещающееся на поверхности кремниевой пластины и функционирующее как электронный ключ (рис. 1.20, а). Обычно он содержит три вывода — источник (эмиттер), сток (коллектор) и затвор (база). Заметим, что в ламповых элементах соответствующие электроды именовались — катод, анод, сетка. Источник и сток образуются путем внедрения в поверхность кремния определенных примесей, а затвор содержит материал, именуемый полисиликоном. Ниже затвора расположен слой диэлектрика, изготовленного из диоксида кремния. Данная структура получила название «кремний-на-изоляторе» (silicon- on-insulator — SOI). Когда к транзистору приложено напряжение, затвор «открыт», и транзистор пропускает ток. Если напряжение снято, затвор «закрыт» и тока нет.

а б

Рис. 1.20. Обычный транзистор (а), терагерц-транзистор (б)

Традиционная технология. Технология микропроцессоров в простейшем случае включает следующие обязательные этапы производства:

• выращивание кремниевых заготовок и получение из них пластин;

• шлифование кремниевых пластин;

• нанесение защитной пленки диэлектрика (Si02);

• нанесение фоторезиста;

• литографический процесс;

• травление;

• диффузию;

• металлизацию.

Все перечисленные этапы используются для того, чтобы на кремниевой основе создать сложную структуру полупроводниковых планарных транзисторов (CMOS-транзисторов) и связать их должным образом между собой.

Процесс изготовления любой микросхемы начинается с выращивания кремниевых монокристаллических болванок цилиндрической формы (кремниевых заготовок). Это лишенный примесей монокристалл.

В дальнейшем из таких монокристаллических заготовок нарезают круглые пластины, «таблетки» (waffer — вафля, облатка), толщина которых составляет приблизительно от 0,2 до 1,0 мм, а диаметр — от 5 см (ранние технологии) до 20 см (современные технологии), поверхность которых отполировывается до зеркального блеска, а затем покрывается тончайшим слоем оксидной пленки (Si02), выполняющей функцию диэлектрика и защитной пленки при дальнейшей обработке кристалла кремния.

После того как кремниевая основа покроется защитной пленкой диоксида кремния, необходимо удалить эту пленку с тех мест, которые будут подвергаться дальнейшей обработке. Удаление пленки осуществляется посредством травления, а для того, чтобы в результате травления оксидная пленка удалялась избирательно, на поверхность пленки наносят слой фоторезиста (состава, чувствительного к воздействию света). Облученные области становятся растворимыми в кислотной среде.

Процесс нанесения фоторезиста и его дальнейшее облучение ультрафиолетом по заданному рисунку называется фотолитографией. Для засветки нужных участков слоя фоторезиста используется шаблон-маска, который содержит рисунок одного из слоев будущей микросхемы. Свет, проходя сквозь такой шаблон, засвечивает только нужные участки поверхности слоя фоторезиста. После облучения фоторезист подвергается проявлению, в результате которого удаляются ненужные участки слоя.

По мере возрастания плотности размещения транзисторов, формируемых в кристалле, литографический процесс усложняется. Минимальная толщина линии, получаемая в процессе литографии, определяется размером пятна, в который удается сфокусировать лазерный луч. Поэтому при производстве современных микропроцессоров для облучения используют ультрафиолетовое излучение. Для производства микросхем по 130-на- нометровому технологическому процессу используется глубокое ультрафиолетовое излучение (Deep UltraViolet — DUV) с длиной волны 248 нм. На подходе литографический процесс с длиной волны 13 нм, получивший название EUV-литографии (Extreme UltraViolet — сверхжесткое ультрафиолетовое излучение). Обычная литографическая технология позволяет наносить шаблон с минимальной шириной проводников 100 нм, а EUV-литография делает возможной печать линий гораздо меньшей ширины — до 30 нм.

После засвечивания слоя фоторезиста осуществляется травление (etching) с целью удаления пленки диоксида кремния. После процедуры травления, т. е. когда оголены нужные области чистого кремния, удаляется оставшаяся часть фотослоя, и на кремниевой основе остается рисунок, выполненный диоксидом кремния.

Процесс внедрения примесей осуществляется посредством диффузии — равномерного внедрения атомов примеси в кристаллическую решетку кремния. Для диффузии легирующей примеси применяется ионная имплантация, которая завершается созданием необходимого слоя полупроводниковой структуры, в котором сосредоточены десятки миллионов транзисторов.

Осуществить требуемую разводку в пределах того же слоя, где расположены сами транзисторы, нереально — неизбежны пересечения между проводниками, потому для соединения транзисторов друг с другом применяют несколько слоев металлизации, т. е. слоев с металлическими проводниками, причем, чем больше транзисторов насчитывается в микросхеме, тем больше слоев металлизации используется (см. рис. 1.23, б).

Для соединения транзисторов друг с другом прежде всего необходимо создать проводящие контакты стоков, истоков и затворов. Для этого по маске в нужных местах вытравливается слой диоксида кремния, и соответствующие окна заполняются атомами металла. Для создания очередного слоя на полученном рисунке схемы выращивается дополнительный тонкий слой диоксида кремния. После этого наносится слой проводящего металла и еще один слой фоторезиста. Ультрафиолетовое излучение пропускается сквозь вторую маску и высвечивает соответствующий рисунок на фоторезисте. Затем опять следуют этапы растворения фоторезиста и травления металла. В результате в новом слое образуются нужные проводящие полоски, напоминающие рельсы, а для межслойных соединений, т. е. соединений слоев друг с другом, в слоях оставляются окна, которые затем заполняются атомами металла. К примеру, при 0,25-микронном технологическом процессе для осуществления разводки используется пять дополнительных слоев.

Процесс нанесения слоев заканчивается, когда схема собрана полностью. Поскольку за один раз на одной «таблетке» создается несколько десятков процессоров, на следующем этапе они разделяются на матрицы (dice), которые тестируются. Если на ранних этапах развития технологий отбраковывалось более 50 % схем, сейчас процент выхода выше, но никогда не достигает 100 %.

Прошедшая тестирование матрица помещается в керамический прямоугольный футляр, из которого выходят «ножки», микроразъемы (pin grid arrays — PGA) интерфейса процессора, с помощью которых процессор помещается и закрепляется в гнезде (socket) на системной плате компьютера (иногда интерфейс оформляется в виде линейного разъема — slot). Количество контактов — от 169 (Socket 1, процессор Intel 80486) до 940 (Socket 940, AMD Opteron). В последнем случае часть соединений зарезервирована для последующего расширения возможностей — размещения на плате процессора кэш-памяти уровня 3 (L3-cache), соединения с другими процессорами (для многопроцессорных систем) и пр.

В настоящее время используется технология микроразъемов (micro pin grid array — (iPGA), существенно снижающая физические размеры интерфейса процессора.

В новом поколении процессоров используются такие нововведения, как SOI-транзисторы (Silicon On Isolator — «кремний на изоляторе»), в которых за счет дополнительного слоя оксида снижаются емкость и токи утечки, а также транзисторы с двумерными затворами и другие новшества, позволяющие повысить быстродействие транзисторов при одновременном уменьшении их геометрических размеров.

Чипы памяти DRAM изготовляются на основе технологии, сходной с изготовлением процессора, — кремниевая основа с нанесенными примесями обрабатывается с маской, которая образует множество пар «транзистор—емкость», каждая из которых размещает 1 бит информации. Стоимость этих схем гораздо ниже, чем процессоров, поскольку они состоят из однородных повторяющихся структур, а также дешевле схем SRAM, поскольку в последних содержится в 2 раза больше транзисторов (каждый бит здесь содержится в триггере, который требует по меньшей мере два транзистора).

Терагерц-технологии. Основная стратегия поставщиков микросхем всегда заключалась в уменьшении размера транзистора (схемного элемента) и повышении плотности упаковки на кристалле. В конечном итоге критическими факторами стали энергопотребление и разогрев платы.

В конце 2002 г. Intel Corporation объявила, что ее инженеры разработали инновационную структуру транзисторов и новые материалы, позволяющие снизить потребление энергии и выделение тепла. Новые структуры получили название Intel TeraHertz transistor (терагерц-транзисторы), в связи с их способностью переключаться со скоростью выше триллиона раз в секунду. Предполагается, что новая технология позволит увеличить плотность в 25 раз, использовать «технологию 20 нм» (элемент схемы в 250 раз меньше толщины человеческого волоса) и разместить на кристалле до миллиарда транзисторов.

Терагерц-транзистор отличается от обычного (см. рис. 1.20, а) тремя важными особенностями (см. рис. 1.20, б):

• источник и сток образуются из более толстых слоев в кремниевой пластине, что уменьшает электрическое сопротивление, потребление электроэнергии и тепловыделение;

• ниже источника и стока помещается сверхтонкий слой изолятора. Это обеспечивает более высокие интенсивности тока в открытом состоянии транзистора и увеличивает скорость переключения. Кроме того, изолятор понижает утечки тока при закрытом транзисторе (в 10 тыс. раз по сравнению с SOI). Это уменьшает вероятность случайного переключения под влиянием блуждающих тепловых электронов и повышает надежность схемы;

• химическое соединение, расположенное между затвором, источником, стоком, заменяется на новый материал «high-к gate dielectric» (оксид алюминия или титана), для нанесения которого используется технология наращивания слоя по одной молекуле.

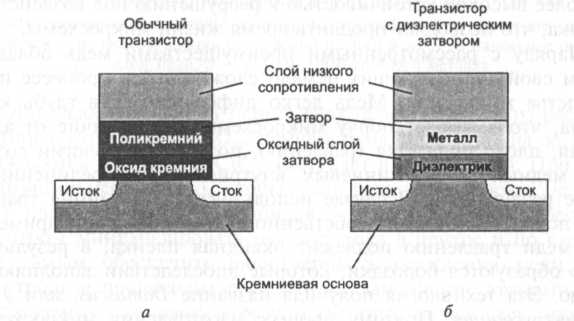

Диэлектрико-металлические затворы транзисторов. Использование затвора из диэлектриков с высокой диэлектрической постоянной (High-k Gate Dielectrics) и металлических электродов затворов транзисторов (Metal Gate Electrodes) было впервые представлено в процессоре Intel Penryn (технология 45 нм) и позволило уменьшить размеры транзисторов и снизить энергопотребление.

В обычном транзисторе снижение толщины слоя диоксида кремния необходимо для уменьшения размера и увеличения плотности размещения транзисторов на кристалле. Однако при достижении определенного предела возникает утечка тока под воздействием «туннельного эффекта» — когда электроны покидают транзистор и рассеиваются, что понижает надежность и увеличивает рассеяние мощности. Поэтому уменьшение размеров ниже данного предела становится нецелесообразным.

Диэлектрик (high-k dielectric или материал с высокой диэлектрической постоянной) в новой технологии замещает слой диоксида кремния в транзисторе и позволяет снизить токи утечки в технологии 45 нм в 5 раз по сравнению с технологией 65 нм.

Относительная легкость использования оксидов кремния в транзисторах ограничивала в течение многих лет применение других материалов при производстве микропроцессоров. Аналогично, традиционная технология использования поликремния для затвора существенно проще, чем внедрение других, возможно более эффективных веществ в процесс производства (рис. 1.21, а).

Рис. 1.21. Обычный транзистор (а); транзистор с диэлектрическим затвором (б)

Использование металлического затвора в процессорах Penryn «сломало» эту традицию; эта технология позволяет улучить эффективность и снизить токи неконтролируемой утечки, поскольку проводимость металлического затвора существенно выше (рис. 1.21, б).

Технология медных проводников. Транзисторы на поверхности чипа — сложная комбинация из кремния, металлов и микродобавок, точно расположенных, чтобы образовать миллионы крохотных переключателей. Поскольку создавались все меньшие и быстрые транзисторы, упакованные все плотнее, их соединение между собой стало превращаться в проблему.

Для установления соединений длительное время использовался алюминий, однако к середине 1990-х гг. стало очевидным, что скоро будут достигнуты технологические и физические пределы существующей технологии. Относительно высокое удельное сопротивление алюминия при уменьшении диаметра проводников приводит к потерям и перегреву схем. Однако длительное время никому не удавалось создать конкурентоспособный чип с медными проводниками.

Основное преимущество медных соединений в данном случае заключается в том, что медь обладает меньшей удельной проводимостью по сравнению с алюминием. При уменьшении площади сечения проводников (с уменьшением размера транзисторов) увеличивается и сопротивление проводников. Кроме того, медные проводники способны выдерживать значительно большую плотность тока, чем алюминиевые, и к тому же обладают более высокой устойчивостью к разрушению под воздействием тока, что позволяет продлить время жизни микросхемы.

Наряду с рассмотренными преимуществами медь обладает рядом свойств, создающих немало сложностей в процессе производства микросхем. Медь легко диффундирует в глубь кристалла, что вызывает порчу микросхемы и, в отличие от алюминия, плохо поддается травлению, поэтому технологии создания медных и алюминиевых внутрислойных соединений в корне различаются. В случае использования алюминия травлению по маске подлежит собственно алюминий, а при применении меди травлению подлежит оксидная пленка, в результате этого образуются бороздки, которые впоследствии заполняются медью. Эта технология получила название Damascus, или узорная инкрустация. Поэтому процесс изготовления микросхем с использованием алюминиевых соединений технологически не совместим с аналогичным процессом с использованием медных соединений.

В сентябре 1998 г. IBM объявила о разработке нового технологического процесса, включающего создание медных проводников на чипе (Damascene процесс — 0,18 мкм CMOS 7SF). Создание каждого нового слоя начинается с получения оксидной пленки, которая покрывается слоем фоторезиста. Далее, посредством литографического процесса, в оксидной пленке вытравливаются бороздки и углубления требуемой формы. Эти бороздки и углубления необходимо заполнить медью. Но прежде, для предотвращения нежелательной диффузии меди, они заполняются тонким слоем антидиффузионного вещества (diffusing barrier), изготовленного из устойчивого материала — титана или нитрида вольфрама. Толщина такой антидиффузионной пленки — всего 10 нм. Микроскопическая начальная пленка меди размещается выше, чтобы удерживать медный слой, который затем наносится на весь чип (рис. 1.22).

Рис. 1.22. Технология медных проводников: а — вытравливание соединений путем фотолитографии; б — нанесение защитного слоя; в — нанесение микроскопической пленки меди; г — нанесение рабочего слоя меди; д — удаление избыточного металла

Для осаждения меди используют гальванизацию из раствора медного купороса Cu2S04, причем сама пластина, на которую осаждаются ионы меди Си++, выступает в роли катода. При гальванизации необходимо, чтобы медь равномерно осаждалась по всей пластине, поэтому подбирают такую плотность электролита, чтобы минимизировать разницу тока в центре и по краям и тем самым обеспечить равномерность осаждения меди. При электролизе происходит постепенное заполнение атомами меди вытравленных канавок, в результате этого образуются проводящие «рельсы». После заполнения медью канавок лишний слой меди удаляется с пластины посредством шлифования, а затем наносится очередной слой оксидной пленки и проводится формирование следующего слоя. В результате образуется многослойная система.

Технологический процесс 65 нм. Intel довела данную технологию до стадии промышленного производства к концу 2005 г. В 65-нм процессе Intel использует УФ-литографию с длиной волны 193 нм, комбинируемую с технологией фазового сдвига. При этом удалось уменьшить до 35 нм эффективную ширину затвора транзисторов (рис. 1.23, а), что приблизительно на 30% меньше, чем при производстве по технологии 90 нм.

Рис. 1.23. Транзисторы поколения 65 нм (в); восемь слоев медных соединений (б)

Остались прежними в новом процессе и используемые для создания транзисторов материалы. Дополнительные усилия были направлены на борьбу с токами утечки. Появившаяся в 90-нм технологическом процессе технология напряженного кремния обрела в 65-нм технологии свою усовершенствованную версию — при сохранении толщины изоляционного слоя затвора на уровне 1,2 нм примерно на 15 % увеличилась деформация каналов транзисторов. Это дало четырехкратное уменьшение токов утечки, которое в конечном итоге создает возможность примерно 30%-ного увеличения частоты срабатывания транзисторов без возрастания их тепловыделения.

И последнее изменение — увеличение числа слоев медных соединений. В новом процессе их восемь, что на один больше, чем в ядрах, выпускаемых по 90-нм процессу (рис. 1.23, б). Благодаря этому Intel надеется упростить проектирование будущих кристаллов.

Печатные платы

Плата, или printed circuit board, — изоляционная пластина, на которой устанавливаются и соединяются друг с другом электронные элементы, перечисленные выше, и приборы меньшей степени интеграции — отдельные транзисторы, резисторы, конденсаторы и др.

Печатная плата изготавливается из пластмассы, гетинакса, текстолита либо другого изолятора (керамика).На плате с одной либо обеих сторон размещаются интегральные схемы, резисторы, диоды и другие полупроводниковые приборы. Для их соединения на поверхности платы наносятся тонкие электропроводящие полоски. Печатная плата может быть двух- либо многослойной.

Существует несколько технологий монтажа элементов (в том числе и интегральных схем) на печатных платах. Наиболее старая из них — монтаж в сквозные отверстия. Здесь элементы создаваемой схемы устанавливаются с одной стороны платы. Вслед за этим появился способ укладки интегральных схем прямо на поверхности этой платы. Вначале интегральные схемы припаивались к печатным платам. Теперь все чаще они приклеиваются без использования припоя. Малая высота интегральных схем, монтируемых на поверхность, позволяет устанавливать их на обеих сторонах платы.

Печатные платы перестают быть только плоскими. Происходит переход от двух измерений к криволинейным поверхностям и созданию печатных дорожек на геометрически изогнутых формах. Все это связано с тем, что по мере усложнения электронных компонентов становится все трудней размещать плоские платы в корпусы, удовлетворяющие требованиям потребителя. Для изготовления основы трехмерных печатных плат используется пластмасса, пригодная для литья.

Для решения задач трассировки соединений на печатных платах применяются средства автоматизированного проектирования (САПР) — программы-трассировщики.