КЛАССИФИКАЦИЯ МЕТОДИК ПРОЕКТИРОВАНИЯ ЭЛЕКТРОННЫХ СХЕМ

Первым фактором, влияющим на специфику проектирования, является тип обрабатываемой информации и связанные с ним методы и способы ее обработки. Проект или его отдельные фрагменты могут включать аналоговые, аналого-цифровые и/или цифро-аналоговые элементы, строиться на основе дискретных (цифровых) компонентов или опираться на встроенные микропроцессорные средства. Отсюда следует многообразие вариантов проектирования, эти варианты в современных технологиях часто называют потоком проектирования (Design Flow). Проектирование при этом может быть цифровым, аналого-цифровым, смешанным цифровым и программным, а также проектированием с ориентацией на синтезируемые цифровые или аналоговые схемы. Возможны и другие комбинации этих вариантов.

Следующим определяющим фактором является выбор технической базы для реализации проекта, а также технологического способа реализации самого проекта. Как правило, одно и то же электронное изделие может быть реализовано различными способами. Здесь должен быть дан ответ на вопрос - будет ли проект построен на стандартных микросхемах или будут использоваться те или иные специализированные ИС и/или комбинация различных типов ИС.

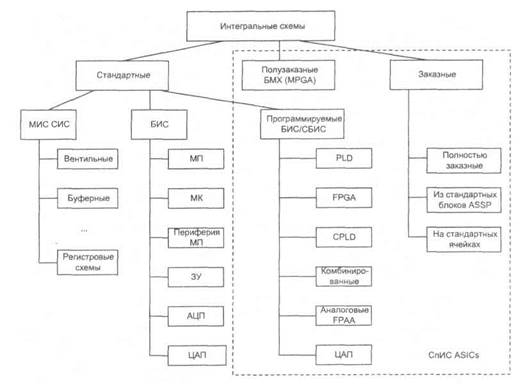

Описание особенностей организации было приведено выше, а классификация ИС по этому признаку приведена на рис. 8.1. Способ изготовления ИС не определяет типы обрабатываемой информации.

Рис.8.1. Классификация ИС по признаку способа изготовления

К стандартным микросхемам отнесены схемы малой и средней степени интеграции -МИС и СИС. Эти микросхемы производятся массовыми тиражами и реализуют стандартные элементы и узлы, функционирование которых никак не определяется конкретными потребителями. К стандартным схемам высокого уровня интеграции (БИС и СБИС) относятся цифровые схемы: микропроцессоры, микроконтроллеры и запоминающие устройства (ЗУ), разнообразные периферийные схемы для МП и МК, включая и аналого-цифровые схемы: аналого-цифровые преобразователи (АЦП), цифроаналоговые преобразователи (ЦАП). Общее свойство этих схем то, что они остаются неизменными после изготовления независимо от устройств и систем, в которых они используются.

К специализированным ИС (СпИС) относятся все, структура которых в отличие от структур стандартных ИС массового производства каким-либо способом приспосабливается к конкретным требованиям того или иного проекта. В английской терминологии СпИС именуются ASICs (Application Specific Integrated Circuits). Среди СпИС различают классы полузаказных и заказных. Разновидностями заказных микросхем являются полностью заказные и спроектированные методом «на стандартных ячейках».

Полностью заказные схемы целиком проектируются по требованиям конкретного заказчика. Проектировщик имеет полную свободу действий, определяя схему по своему усмотрению вплоть до уровня схемных компонентов (отдельных транзисторов и т. п.). Для изготовления схемы требуется разработка всего комплекта фотошаблонов, верификация и отладка всех схемных фрагментов. Такие схемы очень дороги и имеют длительные циклы проектирования.

Схемы на стандартных ячейках отличаются от полностью заказных тем, что их фрагменты берутся из заранее разработанной библиотеки схемных решений. Такие фрагменты уже хорошо отработаны, стоимость и длительность проектирования при этом снижаются. Для производства схем тоже требуется изготовление полного комплекта фотошаблонов, но разработка их облегчена. Потери по сравнению с полностью заказными ИС состоят в том, что проектировщик имеет меньше свободы в построении схемы, т. е. результаты ее оптимизации по таким критериям как площадь кристалла, быстродействие и т. д. менее эффективны. Наивысших технических параметров добиваются от полностью заказных схем, однако метод стандартных ячеек популярен, так как при небольших потерях в технических характеристиках с его помощью можно заметно упростить проектирование схемы. Полностью заказные схемы разрабатываются за время, превышающее время разработки методом стандартных ячеек приблизительно в два раза.

Промежуточное положение занимают схемы, проектируемые по технологии «стандартная продукция для фиксированных приложений» (Application Specific Standard Products -ASSP). Основой технологии является использование в качестве строительных блоков заранее разработанной библиотеки схемных решений системного уровня, таких как микро-контроллеры/DSР-ядра, память, блоки стандартных интерфейсов и блоки специфической системной логики. Для экономической целесообразности реализации подобных проектов для фирмы «Atmel», например, требуется тиражность продукции порядка 100 тыс. кристаллов в заказе.

К полузаказным схемам относятся базовые матричные кристаллы БМК (в английской терминологии MPGA- Mask Programmable Gate Arrays). В этом случае имеется стандартный полуфабрикат, который доводится до готового изделия с помощью индивидуальных межсоединений. Реализация требует изготовления лишь малого числа фотошаблонов. Стоимость и длительность проектирования в данном случае по сравнению с полностью заказными схемами сокращаются в 3-4 раза. Однако результат проектирования еще дальше от оптимального, поскольку в матричных БИС (МАБИС) менее рационально используется площадь кристалла (на кристалле остаются неиспользованные элементы и т. п.), не минимальны длины связей и не максимально быстродействие.

Сходство методов проектирования на БМК и стандартных ячейках состоит в использовании библиотек функциональных элементов. Различие в том, что для схем, проектируемых по методу стандартных ячеек, библиотечный набор элементов имеет более выраженную топологическую свободу. Например, стандартизируется только высота ячеек, а их длины могут быть различными. При проектировании вначале из набора библиотечных элементов подбираются необходимые функциональные блоки, а затем решаются задачи их размещения и трассировки.

Методика, а соответственно и САПР для проектирования по методу стандартных ячеек более сложны, чем для проектирования на основе БМК, которому свойственны более жесткие топологические ограничения. Ограничения вводятся и для метода стандартных ячеек (постоянство высоты ячеек, предопределенность геометрических размеров и положения шин питания, тактирования и др.), но по мере применения более мощных САПР ограничения ослабляются.

Длительность изготовления БИС/СБИС методом стандартных ячеек превышает этот же показатель для МАБИС на основе БМК в 1,3-1,8 раз.

Особое место в классификации занимают БИС/СБИС с программируемой структурой. С одной стороны, они относятся к СпИС, так как в конечном счете приспосабливаются к требованиям конкретного проекта. В то же время этот процесс (конфигурация схемы) не затрагивает изготовителя, для которого схемы являются стандартным продуктом со всеми вытекающими из этого выгодами.