ОБЛАСТИ ПРИМЕНЕНИЯ СПИС РАЗЛИЧНЫХ ТИПОВ

Все типы СпИС имеют свои области применения. Каждому типу свойственно определенное соотношение таких параметров как сложность (достижимый уровень интеграции), быстродействие, стоимость. На выбор типа СпИС для реализации проекта влияет совокупность свойств. Основные соображения можно пояснить с позиций экономики, обратившись к формуле стоимости ИС, которая производится с использованием освоенного технологического процесса:

Сис =Сизг +Спр /N,

где Сизг - стоимость изготовления ИС (стоимость кристалла и других материалов, стоимость технологических операций по изготовлению ИС, контрольных испытаний); затраты на изготовление относятся к каждой ИС, т. е. повторяются столько раз, сколько ИС будет произведено; Спр - стоимость проектирования ИС, т. е. однократные затраты для данного типа ИС; N- объем производства (тиражность), т. е. число ИС, которое будет произведено.

Стоимость проектирования БИС/СБИС велика и может достигать сотен миллионов долларов. Для дорогостоящих вариантов проектирования БИС/СБИС производство становится рентабельным только при большом объеме их продаж.

Затраты Спр и Сизг находятся во взаимосвязи. Рост затрат на проектирование, как правило, ведет к снижению Сизг, поскольку, чем совершеннее проект, тем рациональнее используется площадь кристалла и другие его ресурсы. Отсюда видно, что выигрыш по экономичности могут получать те или иные типы СпИС в зависимости от тиражности их производства N и сложности.

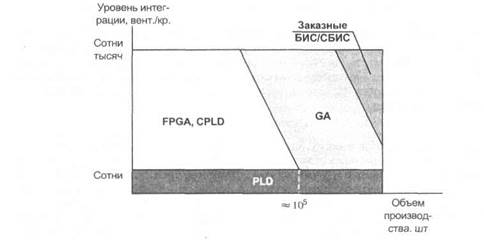

Применительно к микросхемам программируемой логики справедливы следующие положения. Простые устройства со сложностью в сотни эквивалентных вентилей целесообразно реализовывать на PLD (PAL, GAL, PLA). При росте сложности проекта естественен переход к FPGA и CPLD, если тиражность ИС сравнительно невелика. Рост тиражности (приблизительно свыше десятков тысяч) ведет к преимуществам реализаций на БМК, так как стоимость изготовления небольшого числа шаблонов для создания межсоединений разложится на большое число микросхем, а стоимость изготовления каждой ИС уменьшится благодаря исключению из схемы схем программируемых связей и средств их программирования.

При еще большей тиражности выгодным оказывается метод стандартных ячеек, позволяющий дополнительно улучшить параметры схемы, плотнее разместить ее элементы на кристалле, т. е. уменьшить Сизг и улучшить быстродействие. При этом слагаемое Cnр/N в формуле стоимости ИС не окажется слишком большим благодаря большой величине TV, хотя необходимость проектировать весь комплект шаблонов для технологических процессов приводит к большим затратам Спр .

Полностью заказное проектирование для СпИС не характерно. Оно стоит настолько дорого, что применяется практически только для создания стандартных БИС/СБИС массового производства. Например, проектирование первого 32-разрядного микропроцессора обошлось в свое время в 140 млн долл., а ЗУ емкостью в 1 Мбит- в 395 млн долл.

Диаграмма областей целесообразного применения разных типов СпИС в зависимости от их сложности и тиражности приведена на рис. 8.2.

Интересно отметить, что ведущая компьютерная фирма IBM использует методологию проектирования смешанного типа БМК/СЯ (Gate-Array/Standard Cell Intermix), размещая в одной СБИС области, выполненные по методу стандартных ячеек СЯ и по методу БМК. Более плотные и быстродействующие схемы типа СЯ используются в критических трактах обработки сигналов, остальная площадь занимается транзисторами БМК.

Рис. 8.2. Диаграмма областей целесообразного применения различных типов специализированных БИС/СБИС