Триггер задержки (D-триггер)

Триггер задержки имеет единственный входной сигнал, обозначенный буквой D. Значение сигнала на выходе Q такого триггера в такт (t + 1) равно значению сигнала на входе D в предыдущем такте t. Таким образом, входной сигнал передается на выход с задержкой на один такт, т.е.

Qt+1 = Dt.

Асинхронный D-триггер не применяется, так как его выход просто повторяет входной сигнал после окончания режима состязаний. Синхронный же D-триггер функционирует в соответствии с табл. 3.13, из которой видно, что при отсутствии синхроимпульсов (С = 0) состояние триггера остается неизменным. При условии С = 1 триггер передает на выход сигнал, поступивший на его вход в предыдущем такте.

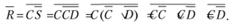

Для синтеза синхронного D-триггера воспользуемся асинхронным RS-триггером. Как видно из таблицы, сигнал на входе D должен воздействовать на триггер только в том случае, когда имеется единичный уровень сигнала С. Следовательно, как и в случае синхронного RS-триггера, на входе D-триггера должны быть двухвходовые элементы И, пропускающие сигнал с входа D, если С = 1.

Таблица 3.13

|

Такт t |

|

Такт t |

|

||||

|

|

|

|

|

|

|

||

|

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

|

0 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

|

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

|

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

Теперь обратимся к правой части таблицы. Переход триггера в состояние единицы должен происходить, когда на входах воздействуют сигналы С = 1 и D = 1. Значит, при таком сочетании сигналов на входе  асинхронного

асинхронного

RS-триггера должен быть нуль, т.е.  . Переход триггера в состояние нуля должен происходить, когда на входах имеется комбинация С = 1, D = 0. Значит, на входе

. Переход триггера в состояние нуля должен происходить, когда на входах имеется комбинация С = 1, D = 0. Значит, на входе  асинхронного RS-триггера при таком сочетании сигналов также должен быть нуль, т.е.

асинхронного RS-триггера при таком сочетании сигналов также должен быть нуль, т.е.  . Поскольку сигнал на входе

. Поскольку сигнал на входе  формируется в момент, когда С = 1, и соответствует инверсному значению D, его можно использовать для формирования сигнала

формируется в момент, когда С = 1, и соответствует инверсному значению D, его можно использовать для формирования сигнала , т.е.

, т.е. . Это же рассуждение можно получить и чисто формально с помощью алгебры логики:

. Это же рассуждение можно получить и чисто формально с помощью алгебры логики:

Следовательно, D-триггер может быть синтезирован на основе асинхронного RS-триггера (рис. 3.30, а, б). Пунктиром обведена схема асинхронного RS-триггера, верхняя схема И-НЕ формирует сигнал на входе асинхронного RS-триггера, а нижняя – на входе

асинхронного RS-триггера, а нижняя – на входе

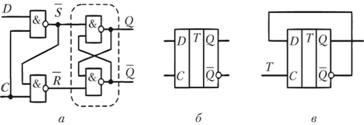

Рис. 3,30. Синхронный D-триггер (а), его условное обозначение (б) и его использование в качестве T-триггера (в)

T-триггер

Булеву функцию, отражающую работу T-триггера, содержательно можно представить так: триггер инвертирует свое предыдущее состояние при подаче по его вход Т единичного сигнала, т.е.  при Т = 1. Соответствующая таблица переключений T-триггера представлена в табл. 3.14. Вход Г называют счетным входом триггера. При подаче на триггер первого единичного сигнала он устанавливается в единицу, при подаче второго – сбрасывается в нуль, третьего – опять в единицу и т.д. Таким образом, изменение выходного сигнала происходит с частотой вдвое меньшей, чем входного. Это позволяет использовать Г-триггер для синтеза двоичных счетчиков, в которых каждый триггер соответствует одному двоичному разряду.

при Т = 1. Соответствующая таблица переключений T-триггера представлена в табл. 3.14. Вход Г называют счетным входом триггера. При подаче на триггер первого единичного сигнала он устанавливается в единицу, при подаче второго – сбрасывается в нуль, третьего – опять в единицу и т.д. Таким образом, изменение выходного сигнала происходит с частотой вдвое меньшей, чем входного. Это позволяет использовать Г-триггер для синтеза двоичных счетчиков, в которых каждый триггер соответствует одному двоичному разряду.

Таблица 3.14

|

Такт t |

Qt+ 1 |

|

|

Tt |

Qt |

|

|

0 |

0 |

0 |

|

1 |

0 |

1 |

|

0 |

1 |

1 |

|

1 |

1 |

0 |

T-триггер может быть синтезирован на логических элементах И-НЕ или ИЛИ-HE, однако чаще всего для этого используют имеющийся в составе серий интегральных микросхем D-триггер. Превращение D-триггера в Τ-триггер осуществляется с помощью соответствующего соединения выводов микросхемы.

Так, если в синхронном D-триггере вход D соединить с инверсным выходом , то он превращается в T-триггер. Действительно, если просмотреть в таблице переключений D-триггера строки, в которых состояние триггера Q меняется на противоположное (см. строки 2 и 3 правой части табл. 3.13), увидим, что значение сигнала на входе D противоположно значению Q. Поскольку сигнал на выходе Q всегда противоположен состоянию Q, то, подавая счетные сигналы Т вместо синхроимпульсов на вход С из D-триггера получаем Τ-триггер (рис. 3.30, в).

, то он превращается в T-триггер. Действительно, если просмотреть в таблице переключений D-триггера строки, в которых состояние триггера Q меняется на противоположное (см. строки 2 и 3 правой части табл. 3.13), увидим, что значение сигнала на входе D противоположно значению Q. Поскольку сигнал на выходе Q всегда противоположен состоянию Q, то, подавая счетные сигналы Т вместо синхроимпульсов на вход С из D-триггера получаем Τ-триггер (рис. 3.30, в).

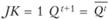

JK-триггер

JK-триггер имеет два входа J и К. Его работа описывается таблицей переключений (табл. 3.15), из которой видно, что при комбинации сигналов J = 1 и К = 1 (третий и седьмой наборы) триггер инвертирует свое предыдущее состояние, т.е. при конъюнкции  . В остальных случаях JK-триггер аналогичен RS-триггеру. При этом вход J эквивалентен входу S, а вход К – входу R.

. В остальных случаях JK-триггер аналогичен RS-триггеру. При этом вход J эквивалентен входу S, а вход К – входу R.

Таблица 3.15

|

Такт t |

|

Такт ί |

|

||||||

|

Номера наборов |

|

|

|

Номера наборов |

|

|

|

||

|

0 |

0 |

0 |

0 |

0 |

4 |

0 |

0 |

1 |

1 |

|

1 |

0 |

1 |

0 |

1 |

5 |

0 |

1 |

1 |

1 |

|

2 |

1 |

0 |

0 |

0 |

6 |

1 |

0 |

1 |

0 |

|

3 |

1 |

1 |

0 |

1 |

7 |

1 |

1 |

1 |

0 |

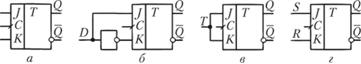

В интегральной схемотехнике распространены синхронные JK-триггеры с динамическим входом синхроимпульсов С (рис. 3.31, а). Эти триггеры путем несложной коммутации (соединения) внешних выводов можно превратить в схемы, выполняющие функции RS-,D-и T-триггера. Поскольку T-триггер меняет свое состояние на противоположное при подаче каждого единичного сигнала на счетный вход Т, используем аналогичное свойство JK-триггера инвертировать свое состояние при одновременной подаче единичных сигналов на входы J и К. Таким образом, для превращения JK-триггера в Т-триггер достаточно соединить входы J и К и подавать на них счетные сигналы Г (рис. 3.31, в).

Чтобы из JК-триггера получить D-триггер, достаточно на вход J подавать прямое значение сигнала D, а на вход К – инверсное, т.е. необходим лишь один инвертор. При этом единичное значение сигнала D будет взводить триггер через вход J, а нулевое – сбрасывать через вход К (рис. 3.31, б).

Наконец, если на вход J подавать сигналы 5, а на вход К – сигналы R, то JK-триггер будет выполнять функции RS-триггера (рис. 3.31, г).

Рис. 3.31. Условное обозначение динамического JK-триггсра (а) и его использование в качестве D-триггера (б), T-триггера (в) и RS-триггсра (г)

Рассмотренные синхронные триггеры являются одноступенчатыми, т.е. содержат один элемент памяти. В их обозначении используется одна буква Т (см. рис. 3.31). Устойчивая работа таких триггеров в схемах с передачей информации между триггерами возможна только при условии, что перевод триггера в новое состояние осуществляется после завершения передачи информации о прежнем его состоянии в следующий за ним триггер. Выполнение этого условия обеспечивается в двухступенчатых триггерах, состоящих из двух одноступенчатых триггеров. Сначала информация записывается в первый триггер (обычно по переднему фронту сигнала С), а затем переписывается во второй (по заднему фронту). Такой принцип построения триггеров иногда называют MS-принципом (master-slave – хозяин-раб). Все рассмотренные типы триггеров могут быть построены по MS-принципу (на схемах их обозначают 7Т).

Триггеры выполняются в виде ИС средней степени интеграции. Обычно они имеют дополнительную логику во входных цепях, благодаря чему обычный триггер может иметь уже не один, а несколько входов. Часть этих входов может использоваться как информационные, а часть – как управляющие (разрешающие или запрещающие запись). ИС триггеров могут иметь входы асинхронной установки R, S, которые воздействуют на элемент памяти триггера непосредственно, минуя входные цепи, и являются доминирующими по отношению к другим входам. В одном корпусе ИС размещается до четырех триггеров, число которых ограничивается количеством выводов микросхемы.