Программируемые контроллеры

При работе микропроцессорной системы часто возникают ситуации, требующие немедленной реакции системы. При этом МП прерывает выполнение основной программы и переходит к обслуживанию ВУ, являющегося причиной возникновения этой ситуации. Обмен информацией между ВУ и МП осуществляется по сигналам-запросам прерывания, поступающим от ВУ. Для работы с прерываниями у МП есть два сигнала: INT – сигнал запроса прерывания от ВУ, являющийся входным для МП, и INTA – сигнал подтверждения прерывания, который выдает МП внешнему устройству, если МП готов к его обслуживанию. В микропроцессорной системе может быть множество различных ВУ, каждое из которых может обращаться с запросом прерывания. Для эффективной работы с прерываниями создаются специальные контроллеры прерываний, обеспечивающие обслуживание ВУ. Эти устройства выполняют всю необходимую работу для организации взаимодействия с ВУ. При этом в начале работы МП осуществляет их программирование, а в процессе работы непосредственно взаимодействует только с контроллером. Таким устройством является БИС Intel 8259А (российский аналог – К1810 BН59). Этот контроллер может обслуживать запросы прерывания от восьми ВУ, а девять каскадно включенных контроллеров – от 64 ВУ.

При работе микропроцессорной системы запросы прерывания от разных ВУ могут накладываться друг на друга. Для разрешения таких конфликтных ситуаций вводится система приоритетов. При этом ВУ выстраиваются в порядке важности: чем важней ВУ для системы, тем выше его приоритет. Если во время выполнения программы обслуживания прерывания от ВУ с низким приоритетом появляется запрос от ВУ с более высоким приоритетом, МП прерывает выполнение программы и переходит к обслуживанию более приоритетного ВУ. Эта процедура может повторяться несколько раз, если запросы прерывания более приоритетных ВУ следуют один за другим. Такое обслуживание прерываний называется вложением прерываний.

Контроллер прерывания (рис. 4.23) через буфер ШД подключается к системной ШД. Все управляющие сигналы, обеспечивающие процессы записи/чтения (ЗП/ЧТ), поступают из МП. Взаимодействие контроллера с ВУ происходит с помощью входов IR, на которые подаются сигналы запросов прерывания от ВУ. Сигналы INT и INTA обеспечивают собственно режим прерывания работы МП.

Работа контроллера прерывания начинается с его инициализации. Контроллер получает команды инициализации по системной ШД от МП. При этом выполняются следующие действия:

• контроллер устанавливается в исходное состояние, в котором все его регистры обнулены;

• устанавливается исходный порядок приоритетов, при котором наивысший приоритет имеет вход IR0, а самый низкий – вход IR7;

• определяются начальные адреса программ обслуживания прерываний, причем процессор заносит адрес программы только для запроса IR0, остальные адреса определяются автоматически, так как располагаются в ОЗУ с интервалом 4 или 8 байтов относительно этого адреса.

Рис. 4.23. Структурная схема контроллера прерываний

Сигналы запросов прерывания поступают в контроллер и запоминаются в регистре запросов прерывания: каждому запросу соответствует свой разряд. Среди полученных запросов выделяется самый приоритетный, который фиксируется в регистре обслуживания запросов. Затем контроллер посылает в МП сигнал прерывания работы процессора INT, и если МП отвечает сигналом INTA (подтверждение прерывания), он формирует так называемый вектор прерывания – начальный адрес программы обслуживаемого прерывания. МП считывает этот адрес и приступает к выполнению программы.

Один контроллер способен обслуживать не более восьми прерываний. Для расширения числа обслуживаемых запросов применяется каскадное включение контроллеров. При этом используются сигналы каскадирования. При таком включении микросхемы контроллеров разделяются на ведущую и ведомые. Ведущая микросхема собирает запросы прерывания со всех ведомых и взаимодействует с процессором. Входы IR ведущей микросхемы подключаются к выходам INT ведомых. Адрес программы обслуживания прерывания формирует ведомая микросхема, а выбор микросхемы, передающей адрес процессору, осуществляет ведущая. Для этого код ведомой микросхемы передается по линиям каскадирования.

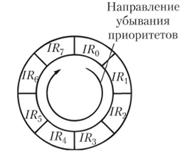

Рис. 4.24. Приоритетное кольцо

При работе микропроцессорной системы возможны ситуации, когда какие-то из ВУ временно могут не обслуживаться. Для того чтобы исключить прерывание работы процессора по запросам таких ВУ, МП запрещает прохождение от них сигналов запросов прерывания. Это делается с помощью специальных команд маскирования прерываний. Маска прерываний – это 8-разрядное слово, каждый разряд которого соответствует одному из сигналов IR. Единица в разряде слова указывает на то, что прохождение соответствующего запроса прерывания должно быть заблокировано. В процессе работы МП заносит в контроллер маску прерываний, которая фиксируется в регистре схемы маскирования и анализа запросов. Если теперь в контроллер поступит запрос прерывания, прохождение которого запрещено, он зафиксируется в регистре запросов, но в регистр обслуживания не попадет и прерывания не вызовет. После снятия запрета, которое также осуществляется с помощью маски, запрос прерывания поступит в регистр обслуживания и вызовет прерывание работы процессора.

В процессе работы возможно также изменение порядка приоритетов сигналов IR. Это осуществляется с помощью установки дна приоритетного кольца (рис. 4.24). В исходном состоянии самый низкий приоритет у сигнала IR7 и дно приоритетного кольца соответствует этому сигналу. При назначении другого сигнала в качестве дна приоритетного кольца, например IR3, все приоритеты смещаются циклически, т.е. сигнал IR4, следующий за IR3, будет теперь иметь наивысший приоритет. За ним приоритеты расположатся следующим образом: IR5, IR6, IR7, IR0, IR1 IR2, IR3.

Процессор может также назначать динамическую установку приоритетов. В этом случае дном приоритетного кольца каждый раз становится последний по времени обслуживания сигнал IR.

Рассмотренный режим работы контроллера называется режимом векторного прерывания, в котором ВУ является инициатором прерывания работы процессора. Возможно также обслуживание ВУ по инициативе процессора. В этом случае контроллер осуществляет только прием сигналов прерывания, их фиксацию и выделение наиболее приоритетного запроса. Вся информация о запросах хранится в слове состояния контроллера. Процессор сам опрашивает контроллер и по слову состояния определяет, есть ли запросы прерывания и от каких ВУ.