Ключевые схемы

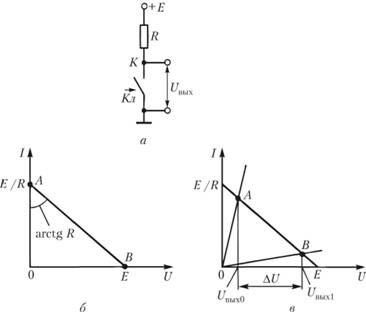

Транзисторные ключевые схемы являются основой всей полупроводниковой цифровой схемотехники. Ключевая схема предназначена для коммутации (переключения) тока в нагрузке и содержит источник напряжения питания, нагрузку (резистор R) и ключ (Кл). Полупроводниковый ключ подобен механическому выключателю (рис. 3.5, а). Если ключ идеален, т.е. его сопротивление в разомкнутом состоянии бесконечно велико, а в замкнутом равно нулю, то ток в цепи при разомкнутом ключе I = 0, а при замкнутом I = E/R. Пусть за выходное напряжение Uвых принято напряжение между корпусом и точкой К. Тогда при разомкнутом ключе, когда падение напряжения на сопротивлении R отсутствует, потенциал точки К будет равен потенциалу источника Е и, следовательно, Uвых = Е.

Когда же ключ замкнут, то падение напряжения на сопротивлении от протекающего по нему тока полностью уравновешивает напряжение источника IR = Е, потенциал точки К равен потенциалу корпуса, принятому за нулевой уровень, и, следовательно, Uвых = 0.

Построив в координатах I–U по точкам Е и Е/R нагрузочную прямую (рис. 3.5, б) и рассматривая ось абсцисс как вольт-амперную характеристику ключа в разомкнутом состоянии, а ось ординат – в замкнутом, придем к выводу, что точка А определяет состояние схемы при замкнутом, а точка В – при разомкнутом ключе. Для идеального ключа коэффициент использования напряжения питания Kи = (UB-UA)/E=1.

Если же ключ неидеальный, то в замкнутом состоянии он обладает хоть небольшим, но внутренним сопротивлением Rвн, а в разомкнутом состоянии – не бесконечно большим, а конечным сопротивлением изоляции Rиз (рис. 3.5, в). Точки А и В пересечения нагрузочной прямой с вольт-амперными характеристиками реального ключа сместятся по сравнению с идеальным ключом, диапазон изменения выходного напряжения уменьшится до значения AU и, значит, коэффициент использования напряжения Kи = ΔU/E< 1.

Рис. 3.5. Ключевая схема (а); ее идеальная (б) и реальная (в) характеристики

Ключевая схема на биполярном транзисторе

В полупроводниковой ключевой схеме роль ключа выполняет биполярный транзистор, включенный по схеме с общим эмиттером, или полевой – по схеме с общим истоком.

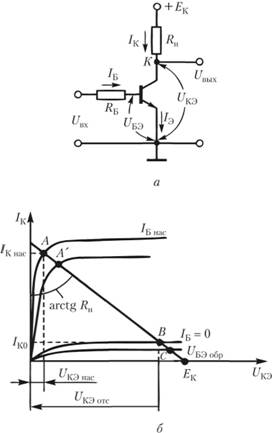

Рассмотрим ключ на биполярном транзисторе (рис. 3.6, а).

Управление таким ключом осуществляет сигнал Uвх. При Uвх = 0 ток базы IБ тоже равен нулю и состояние схемы определяется точкой В (рис. 3.6, б) пересечения нагрузочной прямой с выходной характеристикой транзистора при

Рис. 3.6. Ключевая схема на биполярном транзисторе (а), ее выходные вольт-амперные характеристики (б)

IБ = 0. Транзистор находится в состоянии отсечки, что равносильно разомкнутому ключу, и выходное напряжение, определяемое потенциалом точки К, равно UKЭ отс, т.е. несколько меньше, чем Ек. При UΒΧ, достаточном для создания базового тока IБ нас, переводящего транзистор в режим насыщения, напряжение Uкэ составляет доли вольт. В этом случае состояние схемы определяется точкой А, что равносильно замкнутому ключу, и выходное напряжение равно UКЭ нас, т.е. несколько выше нулевого уровня.

Таким образом, транзистор ведет себя как неидеальный ключ и коэффициент

На подобных ключевых схемах реализуются различные функции алгебры логики. Выясним, какую логическую функцию реализует ключевая схема на рис. 3.6, а. Если на входе ключа высокий потенциал, то транзистор открыт, ток коллектора создает на сопротивлении нагрузки Rн падение напряжения, так что потенциал коллектора – низкий, соответствующий точке А. Напротив, когда на входе ключа низкий потенциал, транзистор закрыт, а на его коллекторе высокий потенциал, соответствующий точке В. Таким образом, ключевая схема инвертирует уровень входного сигнала независимо от того, каким уровнем закодированы нуль и единица.

Следовательно, простейшая ключевая схема на транзисторе с нагрузкой в цепи коллектора, с которого снимается выходное напряжение, является инвертором, реализующим функцию НЕ как в позитивной, так и в негативной логике.

Переключение транзистора из одного состояния в другое происходит не мгновенно, для этого требуется пусть небольшое, но конечное время. Именно это время определяет быстродействие всех цифровых устройств.

При протекании тока через биполярный транзистор в базе происходит накопление неосновных носителей. Причем чем больше коллекторный ток, тем больше носителей к этому моменту должно быть накоплено в базе, т.е. в базе создается заряд qБ. После того как управляющее напряжение UБэ становится запирающим, коллекторный ток IК продолжает еще некоторое время оставаться неизменным за счет избытка носителей в базе. Этот отрезок времени ίρ называют временем рассасывания неосновных носителей из области базы. Лишь после времени tp происходит переход транзистора из состояния насыщения в состояние отсечки и ток IK снижается до уровня IK0, соответствующего запертому состоянию ключевой схемы (точка В на вольт-амперных характеристиках).

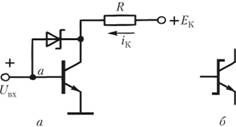

Рис. 3.7. Транзистор Шоттки: принципиальная схема (а), условное обозначение (б)

Этап рассасывания можно устранить, если транзистору после отпирания создать режим, когда он находится на границе между состоянием насыщения и активным режимом работы. Для этого в интегральных схемах используется диод Шоттки, включенный параллельно база-коллекторному переходу транзистора. Такая структура называется транзистором Шоттки (рис. 3.7, а, б).

Напомним, что в активном режиме переход база–коллектор транзистора смещен в обратном направлении (см. параграф 1.3, рис. 1.8, а), т.е. потенциал базы, подключенной к ί/ΒΧ, много ниже потенциала коллектора. С увеличением тока транзистора потенциал коллектора понижается и, приближаясь к насыщению, становится ниже потенциала базы. При этом в базе начинают накапливаться избыточные неосновные носители, увеличивая заряд qБ повышая степень насыщения транзистора. Если бы в схеме на рис. 3.7, а отсутствовал диод, то с увеличением тока потенциал точки b понизился бы настолько, что наступило насыщение транзистора. Этого в схеме не происходит, так как при незначительном (менее 0,1 В) понижении потенциала точки b относительно точки а отпирается диод Шоттки и избыточный заряд qБ удаляется из области базы в коллектор.

Диод Шоттки в интегральном исполнении представляет собой контакт металла с коллекторной областью транзистора и составляет единую структуру. В настоящее время транзистор Шоттки является основой для биполярных цифровых интегральных схем (ИС).

Ключевая схема на комплементарных транзисторах

Полевые транзисторы очень широко используются в цифровых ИС. Так же как и биполярный, полевой транзистор может быть положен в основу транзисторного ключа, реализующего функцию НЕ, т.е. инвертора. Однако если ключ на биполярном транзисторе почти не потребляет мощности только в закрытом состоянии, то на полевых транзисторах можно реализовать ключ, практически не потребляющий мощности от источника питания как в закрытом, так и в открытом состоянии.

Создать на МОП-транзисторах инвертор, не потребляющий мощности при любом сигнале на выходе, позволяют так называемые комплементарные (взаимодополняющие) транзисторы (КМОП), представляющие два МОП-транзистора VT1 и VT2 с каналами противоположного типа, затворы и стоки которых соединены параллельно (рис. 3.8). Схема симметрична: когда один из транзисторов открыт и выполняет роль замкнутого ключа, другой закрыт и служит нагрузочным сопротивлением.

Рассмотрим работу КМОП-транзисторов при позитивной логике и положительной полярности напряжения питания и сигналов. Исток и подложка транзистора VT1 подключены к нулевому потенциалу корпуса, а исток и подложка транзистора VT2 – к потенциалу +Е источника питания. Поэтому при подаче на вход схемы логического нуля (UΒΧ = 0) разность потенциалов между затвором и истоком первого транзистора UЗИ1 = Uвх – 0 = 0 и VT1 заперт. Напряжение между затвором и истоком второго транзистора UЗИ2 = Uвх – Е = 0 – Е = -Е, и транзистор VT2 оказывается в состоянии глубокого насыщения. Через него, как через замкнутый ключ, потенциал +Е подан на выход (UВЫХ ≈ +E), реализуя тем самым на выходе логическую единицу. При этом общий для обоих транзисторов ток Iс близок к нулю, так как сопротивление запертого транзистора VT1 достаточно велико.

Рис. 3.8. Инвертор на КМОП-транзисторах

Если же на вход подана логическая единица (т.е. Uвх ≈ +Е), то UЗИ1 = Uвх – 0 ≈ +E-0 = +E и транзистор VT1 окажется открытым, а транзистор VT2 – закрытым, так как UЗИ2 = UBX – E ≈ +Е – Е ≈ 0. Значит, через замкнутый ключ VT1 на выход будет подан нулевой потенциал корпуса Uвых ≈ 0, реализуя на выходе логический нуль. При этом общий ток /с останется близким к нулю, потому что будет достаточно большим сопротивление запертого транзистора VT2.

Таким образом, в любом статическом состоянии схема практически не потребляет мощности от источника питания. Ток через оба транзистора будет протекать только во время переключения, когда один из транзисторов еще не закроется, а другой – уже приоткроется.

Ключевая схема на КМОП-транзисторах близка к идеальному ключу, и коэффициент использования напряжения источника питания в таком инверторе Ки = Uвыx/E ≈ 1.

Работоспособность такого инвертора не зависит от напряжения питания при условии, что оно не меньше удвоенного значения порогового напряжения транзистора (E ≥ 2UЗИ пор), поэтому схема может работать при больших разбросах напряжения питания.

Благодаря высокому значению коэффициента использования напряжения питания, малой потребляемой мощности и высокому быстродействию ключевые схемы на КМОП-транзисторах нашли широкое применение в интегральной схемотехнике.