Сложные программируемые логические устройства (CPLD)

Архитектурно микросхема класса CPLD состоит из центральной коммутационной матрицы, множества функциональных блоков, в которых осуществляется вся логическая обработка сигналов, и блоков ввода/вывода, расположенных на периферии кристалла и осуществляющих прием и передачу сигналов между кристаллом микросхемы и контактными площадками. Одной из ведущих фирм по производству микросхем класса CPLD является фирма Altera, а семейство микросхем МАХ этой фирмы является классическим примером данного направления ПЛИС. Первая микросхема этого семейства была анонсирована в 1995 г. и была реализована на основе технологии 0,5 мкм. В настоящее время фирма Altera продолжает выпускать микросхемы семейства МАХ, которое насчитывает уже пять подсемейств. Это МАХ 7000, появившееся в 1995 г., МАХ 3000 (2002 г.), МАХ 11 (2004 г.), MAX II Z (2007 г.) и МАХ V (2010 г.). Последнее подсемейство было реализовано по технологии 0,18 мкм. Рассмотрим архитектуру микросхем CPLD на примере архитектуры микросхемы МАХ 7000.

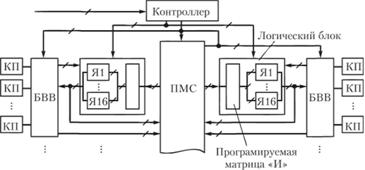

На рис. 4.34 представлен фрагмент структуры CPLD МАХ 7000. Центральная коммутационная матрица здесь именуется программируемой матрицей связи (ПМС), функциональные блоки – логическими блоками (ЛБ). У младшего представителя CPLD было только два ЛБ. С повышением сложности микросхем число ЛБ увеличивалось, при этом структура микросхемы в целом составлялась повторением изображенного на фрагменте яруса, состоящего из двух ЛБ, двух блоков ввода/вывода (БВВ) и набора контактных площадок, расположенных слева и справа от ПМС. Старший представитель CPLD МАХ 7000 содержит шестнадцать таких ярусов, т.е. 32 Л Б, а последние представители MAX V – 1700 Л Б.

Рис. 4.34. Фрагмент структуры CPLD МАХ 7000

Вся коммутация сигналов внутри кристалла выполняется ПМС. Эта матрица содержит набор пересекающихся вертикальных и горизонтальных линий связи.

Горизонтальные линии соединены с ЛБ, а также БВВ. Часть горизонтальных линий является входными, а часть – выходными. Сигнал с входных линий на выходные передается через вертикальные линии матрицы соединений, при этом коммутация сигнала с одной линии на другую осуществляется не через программируемый ключ (в отличие от FPGA), а через двухвходовую схему "И". Для этого к одному из ее входов подключается линия-источник, к выходу – линия-приемник, а ко второму входу – программируемый транзистор. Для того чтобы сигнал проходил с одной линии на другую, необходимо запрограммировать транзистор таким образом, чтобы через него на второй вход схемы "И" подавался разрешающий уровень лог. 1. Скорость распространения цифрового сигнала с входа конъюнктора на выход гораздо выше, чем через ключевой транзистор, поэтому использование вместо ключей управляемых конъюнкторов дает выигрыш в быстродействии микросхем CPLD. Вертикальные линии матрицы тянутся через все горизонтальные и могут быть подключены к любой входной линии; таким образом, любой вход матрицы может быть подключен к любому выходу, т.е. ПМС обеспечивает полную коммутируемость блоков CPLD. В микросхемах подсемейств МАХ 7000 и МАХ 3000 для программирования конфигурации использовались ячейки EEPROM, в МАХ И, MAX II Z и MAX V – флэш-память. Поэтому, в отличие от ПЛИС FPGA фирмы Altera, ПЛИС CPLD хранят свою запрограммированную конфигурацию и после снятия напряжения питания.

Логические блоки осуществляют вычисление логических функций, но также имеют возможность хранения полученного результата в триггерах. В единую схему устройства они объединяются с помощью ПМС. ЛБ состоит из программируемой матрицы И и шестнадцати макроячеек (macrocells) – Я1:Я16. В программируемой матрице И, так же как и в ПЛМ, осуществляется формирование термов (см. рис. 4.27, а). Термы формируются сразу для всех макроячеек, но на вход каждой из них поступают свои термы, необходимые для реализации логической функции путем сборки термов по "ИЛИ". В макроячейке возможна прямая выдача вычисленного значения логической функции на выход, что используется для синтеза чисто комбинационных устройств. Для синтеза последовательностных устройств в макроячейке имеется триггер. В этом случае результат логической операции записывается в триггер и его выход подключается к выходу макроячейки. Синхронизация работы триггера, а также его асинхронная установка и сброс могут осуществляться как контроллером, так и с помощью термов, поступающих от программируемой матрицы. Кроме того, триггер макроячейки можно использовать для ввода внешних сигналов непосредственно с контактной площадки, минуя БВВ и ПМС. Такие цепи называют цепями быстрого ввода.

При синтезе последовательностных цифровых устройств (например, счетчиков) триггеры большей части макроячеек формируют промежуточный результат, который используется для дальнейшей обработки. В этом случае выход макроячейки поступает в ПМС. Если в макроячейке сформировался готовый выходной сигнал синтезируемого устройства, то ее выход подключается к БВВ. Все описанные функции, выполняемые макроячейкой, программируются.

В ПЛИС типа CPLD имеется набор глобальных управляющих сигналов, которые поступают одновременно на все ЛБ. Это сигналы тактирования, сброса и разрешения выхода. С их помощью обеспечивается синхронная работа всего синтезированного на основе CPLD устройства.