ПРИНЦИПИАЛЬНАЯ СХЕМА УСТРОЙСТВА СИНХРОНИЗАЦИИ

КУРСОВАЯ РАБОТА

«ПРОЕКТИРОВАНИЕ ЦИФРОВЫХ УСТРОЙСТВ СИНХРОНИЗАЦИИ»

Выполнил:

студент гр. ТКд-31

Кузнецов В.М.

Проверил преподаватель: Горохин В. Н.

Ульяновск 2012

ВВЕДЕНИЕ.

В последние годы количество цифровых систем управления и обработки информации постоянно увеличивается. В связи с этим постоянно поднимается вопрос о взаимной синхронизации отдельных узлов этих систем между собой и взаимной стыковки и синхронизации таких систем. В курсовой работе проводится разработка устройства синхронизации по условиям, приведенным в задании.

Задание на курсовую работу.

Задание к курсовой работе состоит из требований к выходным сигналам устройства, которые приведены в таблице

Таблица 1

| Вых. сигналы | Ts, мкс | T, мкс | Tn, мкс | Активный уровень |

| T1 | 1.5 | |||

| T2 | ||||

| T3 | 2/3 | 2/3 | ||

| STR1 | ||||

| STR2 | 2.5 | |||

| STR3 | ||||

| F1 | ||||

| F2 | ||||

| F3 |

Приняты следующие условные обозначения:

Т1... ТЗ - выходные импульсы устройства

STR1... STR3 - выходные стробы устройства

F1... F3 - выходные частоты устройства

Т - длительность (мкс)

Ts - время задержки (мкс)

Tn - период повторения (мкс)

ВЫБОР ЧАСТОТЫ ТАКТОВОГО ГЕНЕРАТОРА

Согласно заданию период повторения выходных последовательностей равен 92 мкс. Задание включает в себя только целочисленные значения временных характеристик импульсов. Следовательно, необходимо будет использовать тактовый генератор частотой 1 МГц.

ОПИСАНИЕ ФУНКЦИОНАЛЬНОЙ СХЕМЫ

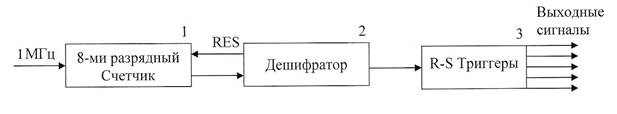

Схема устройства (рис.1) представляет собой счётчик 1 с коэффициентом пересчёта заданным дешифратором 2, при заполнении счётчика до N на выходе дешифратора появляется сигнал сброса счётчика RES, после чего цикл счёта повторяется.

Период счётчика равен произведению коэффициента пересчёта на период входных импульсов t. Сбрасывается в исходное состояние по сигналу с дешифратора через время равное nl*t, где n1 - количество тактов генератора, которые укладываются в длительности первого импульса. Сигнал Т2 активизируется через Ts/t входных импульсов, сбрасывается он через Ts+T/t тактов. Аналогично происходит с импульсами STR1, STR2, SТRЗ за исключением того, что выходной сигнал проинвертирован.

Рассмотрим несколько подробнее управление сигналом T3. При входном сигнале КОМ_ТЗ низкого уровня триггер T3 устанавливается через время задержки 2 мкс и сбрасывается через время 2 мкс, при установке сигнала ком_T3 в «1» этот триггер устанавливается через время задержки З мкс и сбрасывается через время З мкс.

Выходные последовательности F1, F2, FЗ берем получения их с отдельного счетчика.

Рис.1. Функциональная схема устройства синхронизации.

ОПИСАНИЕ ПРИНЦИПИАЛЬНОЙ СХЕМЫ

На ИМС DD2 собрана счётная линейка, по прошествии 92 мкс от момента перехода счётчика через 0 в счётчике будет записано 92. Дешифратор собран на ИМС DD3, DD4, каждая ИМС дешифрирует свою половину байта. Сигнал ТЗ управляется с помощью микросхемы DD16. ИМС DD5 является отдельным счетчиком, с которого получаем сигналы F1, F2, FЗ.

ПРИЛОЖЕНИЕ 1

ПРИНЦИПИАЛЬНАЯ СХЕМА УСТРОЙСТВА СИНХРОНИЗАЦИИ

ПРИЛОЖЕНИЕ 2